Automated Power Model Verification for Analog IPs

By Sierene Aymen and Hartmut Marquardt, Mentor Graphics

Eliminating manual work during power intent verification of analog IPs reduces susceptibility to risks created by human error.

Creating macro power models for analog intellectual property (IP) blocks is essential to enable the chip assembly group to effectively integrate these blocks within their place and route environment. These macro models, which define power domains, identify IP ports as signal, power, ground, or trivial ports, and describe the associations of signal pins to power supply pins. Due to their complexity, and the unlimited design freedom of full custom designs, there is no algorithmic solution for the automated generation of these macro power models, so they must be developed manually by designers. However, that leaves them susceptible to human mistakes and oversight. Errors in these power models can have a wide array of possible effects on the circuitry, from slight performance effects to extreme damage to the IPs.

However, developing an automated flow for power intent verification is not only possible, but practical. By automating the verification of macro power models we can at least find and eliminate any errors in a timely and accurate manner during circuit qualification.

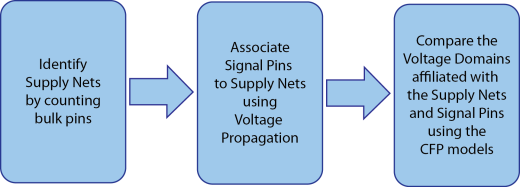

Achieving automated power model verification requires the ability to read the data generated for the macro models, understand the power intent and the connectivity of the design, and verify the power models accordingly. The overall flow is based on power information parsed from common power format (CPF) files, as well as propagation rules that describe the power intent (Figure 1).

Figure 1. Main modules comprising an automated power intent verification flow.

To illustrate how such an automated approach works, we’ll walk through the process using the capabilities of the Calibre PERC reliability platform and its voltage propagation framework. The tool first identifies the power domains of all available pins. Supply net candidates are identified based on connected bulk pin counts. If the majority are PMOS bulk pins, then the net connected to the cell port is probably a power net, whereas if the majority are NMOS bulk pins, the net is probably a ground net.

The tool then relates the signal pins to supply nets using its voltage propagation functionality. Voltage propagation rules are defined across the devices, based on the design intent. The tool creates an error if an ambiguous supply relationship is found. In addition, top-level supply clamps are marked, and errors are generated if the internal supply nets receive no signals.

In this automated verification flow, information about the power domains of custom IP blocks is provided as macro models that reflect the design intent within the input CPF. These macro models are loaded with information concerning the power domains, such as instances and ports belonging to each power domain. The Calibre PERC flow automatically captures the relevant information to be exploited when applying the CPF definitions on all ports.

Last, the Calibre PERC tool verifies the CPF supply definitions by ensuring that the CPF power and ground definitions match the bulk pin statistics compiled earlier within the flow. It also verifies that the high bulk pin count nets are associated with the proper CPF definitions.

Output is presented in a simple spreadsheet format (Table 1), where each port within the analog IP block is captured and its connectivity is displayed. In particular, the tool determines whether each port is a signal port or a supply port, using the macro models in conjunction with the propagation rules. If it is a supply port, it is further identified as either a power port or a ground port. The power and ground domains each signal port belongs to is also specified.

Table 1: csv format output file

With an automated power model verification process, designers can now quickly and accurately verify the power models for the analog IP blocks with only a minimal amount of input needed to describe the voltage propagation criteria. This information, in conjunction with the rules that quantify the power intent within the power format files, provides designers with the information they need to perform the extensive power verification process.

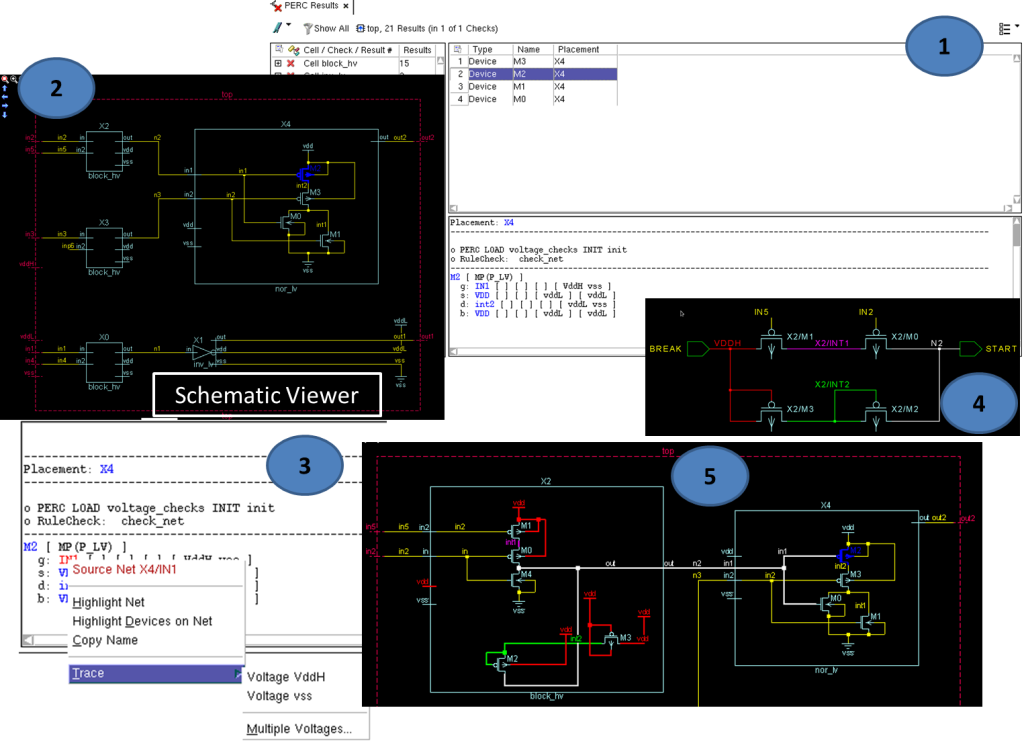

Throughout the power intent verification flow, interactive debugging capabilities are offered, minimizing the traditional lengthy review process. The Calibre RVE tool provides visual voltage propagation, where voltages can be traced across all the pins, showing how voltages propagate and terminate. This capability provides designers with better understanding of their IP blocks, and helps them easily validate their macro models and identify any areas that violate their power intent (Figure 2).

Figure 2: Visual voltage propagation interactive debugging using Calibre PERC and Calibre RVE tools.

Both the CPF and unified power format (UPF) standard power specification formats are required to ensure correct connectivity of custom analog IP blocks during chip assembly. By enabling a topology check of the schematic netlist during circuit qualification, the automated voltage propagation functionality in the Calibre PERC tool enables analog designers to minimize both errors and time to market. With its full coverage, fast runtimes, and flexible graphical debugging capabilities, designers using such an automated power intent verification flow can be confident that the macro power models they generate are accurate and complete.

Authors

Sierene Aymen is a Technical Marketing Engineer for Calibre Design Solutions at Mentor Graphics Egypt.

Hartmut Marquardt is a Senior Application Engineer at Mentor Graphics Germany.

Liked this article? Then try this –

This article was originally published on www.seminengineering.com