Using Body Bias in High Performance, Low Power Electronics

By Flint Yoder – Mentor, A Siemens Business

The body bias effect is used to tune circuit behavior to meet power and performance specifications, but getting it right isn’t easy. Accurate, fast, automated body bias verification is critical to success.

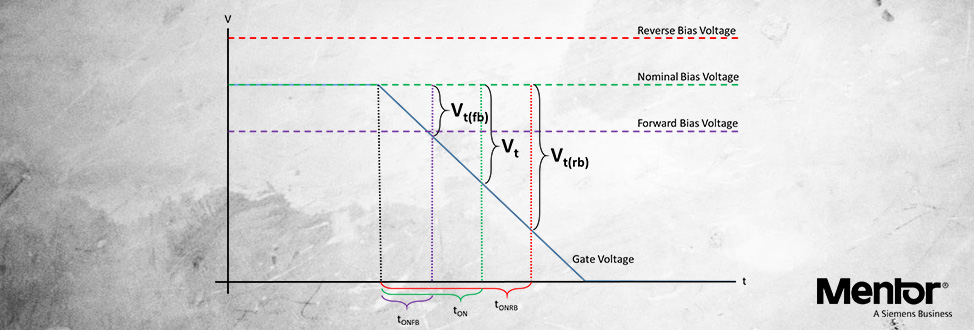

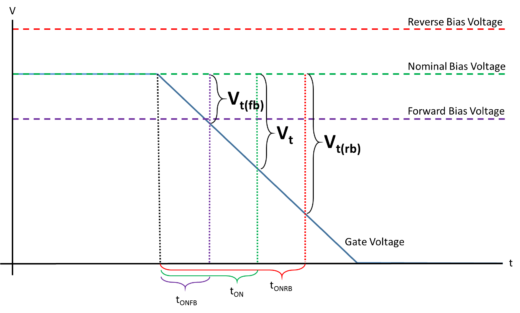

Body bias is a technique used to dynamically adjust the threshold voltage (Vt) of a CMOS transistor, which allows a designer to tune a circuit’s behavior to meet both the power and performance specifications. By altering the voltage of a device’s bulk connection, the designer can place a device into either reverse or forward body bias, changing the effective Vt required to turn the device on.

While this application of body bias can be extremely beneficial in high performance, low power designs, designers must thoroughly understand the requirements of a given design to ensure the bias conditions of all devices within a design are properly set. Incorrect use of body bias can degrade, rather than improve, the performance of the IC. Depending on the extent of the problem, the mistake can end up being a reliability concern, or can cause the part to no longer meet the required specifications.

When multiple power domains are introduced into a design, the possibility of a device being connected to an incorrect domain increases. This potential only grows greater as the size of each design and the number of domains increases, and specific forward or reverse biasing domains are introduced. Without a proper verification methodology in place, the overall quality of a product quickly becomes suspect.

When multiple power domains are introduced into a design, the possibility of a device being connected to an incorrect domain increases. This potential only grows greater as the size of each design and the number of domains increases, and specific forward or reverse biasing domains are introduced. Without a proper verification methodology in place, the overall quality of a product quickly becomes suspect.

While the most basic validation process is a visual inspection of the design, increasing design complexity makes it progressively more difficult to have full confidence in a manual validation process. As part of a complete reliability verification solution, the Calibre® PERC™ reliability platform provides a comprehensive and accurate body bias verification process. The Calibre PERC programmatic approach to reliability checks employs an efficient static topological analysis, which can be performed on either schematic or layout input data, ensuring that all circuitry of interest is automatically identified and appropriately analyzed. Enhanced debugging features help reduce design cycle turnaround time, while giving designers confidence that all body bias conditions have been accurately assessed throughout the design.

To get the full story on the body bias effect, and how the Calibre PERC reliability platform can help you apply it to the best advantage in your designs, check out our white paper, Automated Body Bias Validation for High Performance, Low Power Electronics.