Simplify and speed up early floorplan verification with incremental interface DRC

By James Paris – Mentor, A Siemens Business

In early floorplan verification, incomplete blocks produce numerous interface errors. Incremental interface DRC checking removes these false errors, shortening DRC runtime and debug sessions during block implementation.

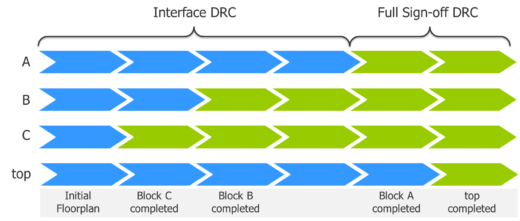

Chip-level physical implementation teams are responsible for managing top-level physical verification, starting from the early floorplanning stages all the way through tapeout. However, in early floorplanning, many blocks placed in the chip-level floorplan may still be under development. Merging these incomplete blocks with the chip-level interconnect for sign-off DRC typically produces a massive number of errors from the block core and along the block boundary at the chip-level interface, most of which are due solely to the incomplete blocks. Finding and fixing the valid errors without wasting time on false errors is essential to both sanity and schedules.

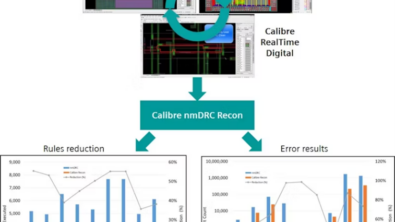

The ideal solution would enable chip-level designers to validate the chip-level interconnect and block interfaces in their floorplan without generating those mountains of invalid DRC results. Design teams seeking that extra edge in time to market can achieve significant time savings by augmenting existing sign-off DRC flows with incremental interface DRC checking that excludes rules and data that cannot be reliably checked when blocks are incomplete.

Sign-off verification flows assume the input design databases are complete. Calibre sign-off DRC decks contain the complete set of rules required to validate full-chip data, blocks, and single cells. Chip-level check requirements require both cell and block-level checks, as well as density and antenna checks, or other chip-level checks, to meet sign-off criteria.

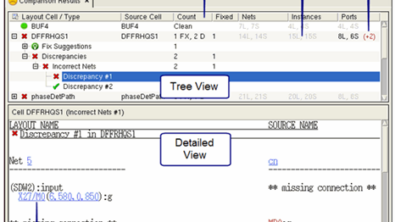

Interface DRC check requirements differ from both, lying somewhere between the two. An interface DRC checking flow will not always have completed GDS or OASIS blocks, although the footprint, pin locations, and some interconnect will already exist. The block core might include placements or interconnect, depending on progress made on each individual block. Excluding the incomplete block cores while including the block periphery during interface DRC checking finds and reports any contextual violations to the chip-level designer, but avoids output from the core (which the designer cannot fix).

Interface checking simplifies the verification flow by selectively running chip-level checks only, which generate valid results on incomplete design data, and only checking the edges of incomplete blocks in their chip-level context. The key elements required to implement an interface DRC flow are 1) to determine when to enable or disable specific chip-level checks, and 2) to exclude data from incomplete blocks or cores from being included in DRC checking or results output.

If you’d like to learn more about implementing interface DRC checking for early validation of chip-level designs, avoidance of costly rework, and an easy transition to full sign-off verification, check out our white paper, What designers need to know about chip-level interface physical verification.

If you’d like to learn more about implementing interface DRC checking for early validation of chip-level designs, avoidance of costly rework, and an easy transition to full sign-off verification, check out our white paper, What designers need to know about chip-level interface physical verification.