Context-aware verification checks enhance checking and debugging capabilities

By Sherif Hany – Mentor, A Siemens Business

Automated context-aware verification helps designers ensure the performance and reliability of complex designs within today’s tight delivery schedules.

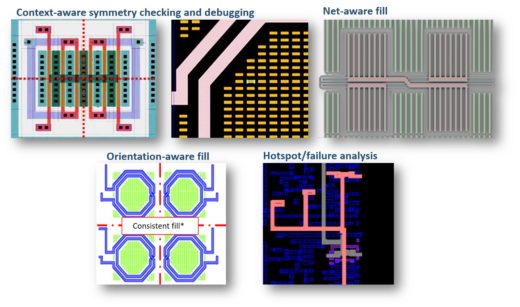

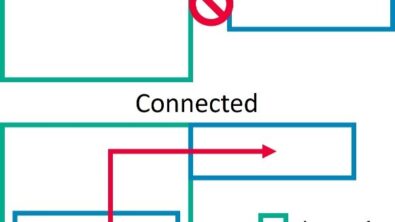

Context-aware verification is enabling designers to evaluate complex design conditions quickly and accurately at both established and emerging process nodes. Context-aware checks combine the physical layout of a component with its electrical implementation to go beyond simple polygon width, spacing, and run length requirements, and consider the nets enclosing those polygons and their associated voltage domains when determining check compliance. This allows designers to check and debug a wide range of design conditions, from advanced design rule compliance to circuit and reliability verification to design optimization and finishing.

Although a limited concept of context-aware checking has been around for a while, invoking these primitive context-aware checks without automated support requires the designer to analyze and select the electrical components, cross-reference them between front/back-ends, and manually add marker layers and layout annotations, which is time-consuming and subject to human error. Given the growth in the type and number of context-aware checks, the manual approach is no longer viable (if it ever truly was).

A broader and more detailed concept of context-aware checking, combined with new automation capabilities in EDA tools, has sparked new implementations of context-aware verification. Similar to the evolution in the design phase that required new layout-aware design techniques, where both the front-end (schematic) and back-end (layout) are implemented simultaneously to account for layout proximity effects and stress parameters, automating context-aware checks means they are no longer limited to geometrical checking, but can now be integrated with every stage in the design and verification cycle.

In addition to enhanced verification, the context-aware information can be provided during debugging to give designers the details they need to precisely and accurately adjust the layout. For example, in voltage-aware DRC, spacing violations are no longer between two polygons, but between two nets annotated by their source information and topological groups. Context-aware symmetry checking enables topological/electrical patterns to be evaluated for symmetry, similar to the way geometrical patterns are compared. In failure analysis, hotspot/defect results can be associated with their interacting nets, devices, and even their voltage domains. This actionable feedback improves the quality, accuracy, and turnaround time of debugging.

Want to learn more? Download a copy of our white paper, Beyond geometry checks: Context-aware design verification, for all the juicy details.