Inductance parasitics: the enemy of analog/RF performance and reliability

By Hossam Sarhan – Mentor, A Siemens Business

Ignoring interconnect inductance extraction in analog and RC designs can be a fatal error. Learn why inductance extraction for interconnect is now essential for accurate post-layout simulations.

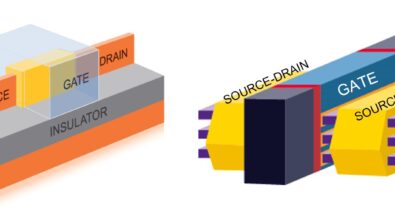

Analog and radio frequency (RF) chips are the hardware backbone supporting today’s high-frequency communication technologies. With frequency ranges for 5G communication exceeding 40Ghz, parasitics can significantly affect the performance of these chips. Designers must ensure analog/RF designs take into account post-layout resistance, capacitance, and inductance parasitics to confirm design simulation results match the silicon-fabricated results.

Inductance parasitics? Yes! Although inductance extraction was primarily limited to custom inductor characterization in the past, that’s no longer enough for today’s analog/RF designs. Inductance extraction for interconnect is now essential to ensuring accurate post-layout simulations.

Inductance parasitics occur due to the magnetic field generated by currents passing through conductors. These parasitics can have several impacts on chip performance, ranging from signal delay, ringing (signal oscillation), and overshooting (exceeding target values) to reflections in transmission lines or drifting of oscillating frequency.

Designers face two main challenges in inductance extraction:

- Inductance has a long-range effect. The magnetic field is not terminated on neighboring conductors.

- Inductance is a property of current loops, and it can be difficult to determine which current loops are significant.

The primary methodologies used for inductance extraction are loop inductance and partial element equivalent circuit (PEEC). The loop method computes inductance with return paths, while the PEEC method computes inductance for a straight wire segment carrying current.

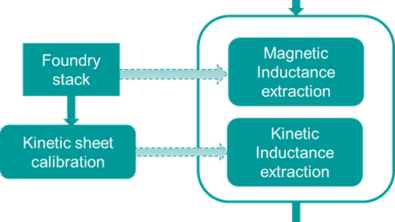

The Calibre xL extraction tool provides a fast, accurate field solver-based inductance extraction engine that can use both loop and PEEC methods to extract both self and mutual inductance parasitics of on-chip interconnects. It is also fully integrated with other Calibre extraction tools to generate a single RCCLK netlist.

If you work on analog or RF designs, and you want to deliver chips that provide the highest level of circuit performance and reliability, you need to add inductance extraction to your checklist. Learn more about inductance parasitics and their extraction by downloading a copy of our white paper, Interconnect inductance extraction for analog and RF IC designs.