Do you have all the data required for HDAP LVS? Not sure? That’s okay!

By Tarek Ramadan – Mentor, A Siemens Business

Automated LVS/LVL verification for HDAP isn’t quite a mature process yet, but available tools and flows can still provide useful data to HDAP designers. Learn more…

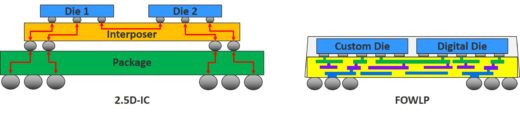

High density advanced packaging (HDAP) designs are the newest breed of integrated circuit (IC) packaging, with cost, risk, and scaling limitations being the primary factors behind the growth of these multi-die solutions. HDAP designs such as 2.5D interposer-based packages and fan-out wafer-level packages are driving a convergence between the traditional IC design and IC package design worlds.

While a lot of sweat equity has gone into analyzing the issues and developing automated electronic design automation (EDA) solutions for HDAP verification, it’s safe to say this is still a young and developing solution space. Case in point: layout vs. schematic (LVS) and layout vs. layout (LVL) package verification.

All IC and system-on-chip (SoC) designers know you can’t get to tapeout unless the physical layout of your design accurately implements the designed connectivity (schematic). LVS verification is a cornerstone of the IC verification process. The design company creates the source netlist and the layout database, and uses an LVS rule deck from the foundry in conjunction with mature, qualified EDA tools to ensure the physical circuitry will operate as intended.

HDAP LVS operates a little differently. First of all, there’s no industry agreement on who provides the necessary inputs, or what some of those inputs even look like. To get around these issues, EDA companies are providing “flexible” HDAP LVS/LVL verification, in the sense that there is always some type of LVS/LVL verification that can be performed with the available data. No source netlist? How about open/short checking? No layout design databases for the dies? Use assembly-level LVS tools with die bump coordinates and pin names to create a “die placeholder” database to use in the package layout design database. By combining the capabilities of both package and IC verification tools, Mentor provides complete automated flows for both LVS and assembly-level LVL verification.

Whether you’re an IC/SoC designer supplying dies for an HDAP design, or an HDAP designer learning new techniques and using new tools (and old tools in new ways), our white paper, A deep dive into HDAP LVS/LVL verification, can not only give you a better understanding of the specific challenges of HDAP verification, but also provide insight into how these new approaches can help you complete your HDAP designs with confidence.

Whether you’re an IC/SoC designer supplying dies for an HDAP design, or an HDAP designer learning new techniques and using new tools (and old tools in new ways), our white paper, A deep dive into HDAP LVS/LVL verification, can not only give you a better understanding of the specific challenges of HDAP verification, but also provide insight into how these new approaches can help you complete your HDAP designs with confidence.