MaxLinear and Calibre RealTime Digital in-design DRC: a winning combination

By Srinivas Velivala – Mentor, A Siemens Business

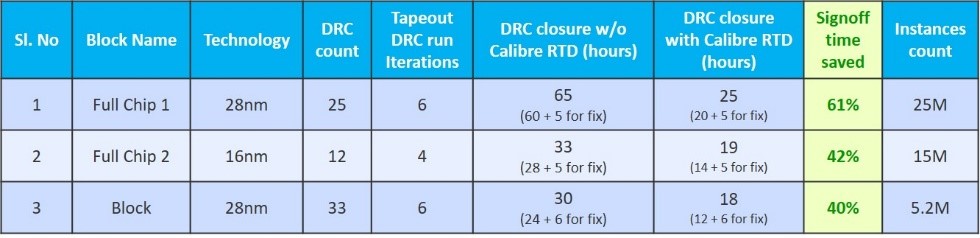

MaxLinear implemented the Calibre RealTime Digital interface for fast, iterative signoff DRC during P&R, and shaved weeks off tapeout schedules while meeting PPA targets. Learn how they did it…

At the 2019 TSMC OIP Forum, the Customers’ Choice Award for best paper was awarded to the joint paper from MaxLinear and Mentor, a Siemens business, titled:

“Optimize SOC designs while enabling faster tapeouts by closing chip integration DRC issues early in the design cycle”

The paper was presented at the TSMC OIP Ecosystem Forum North America on September 26, 2019, and received the highest average scores by the attendees.

MaxLinear, Inc. is a pioneer in low-power CMOS radio frequency (RF) and analog/mixed-signal (AMS) integrated circuits (ICs) for the connected home, wired and wireless infrastructures, and industrial and multi-market applications. One market focus is their digital signal processing (DSP) system-on-chip (SoC) solution that serves the high-speed optical interconnect needs of mega-scale cloud and enterprise data centers. These DSP chips are expected to work for 10 years or more, meaning both reliability and manufacturability (yield) are critical components of a successful DSP design process. At the same time, MaxLinear engineers must strive to achieve their power, performance, and area (PPA) design goals to ensure they produce the most efficient chip possible.

One of the obstacles they faced was the impact of automated design enhancements during place and route (P&R) creating complex design rule checking (DRC) errors that typically required time-consuming manual debugging and multiple DRC iterations to confirm correction during DRC closure. In addition, P&R internal DRC solutions generally don’t recognize or flag some types of DRC violations, such as those introduced by:

- Manual DRC error fixes

- Last-minute functional/timing ECO changes

- Final via swaps made to improve DFM scores

MaxLinear was looking for a solution that improved their DRC closure time, while enabling their designers to meet not only design reliability and manufacturability requirements, but also their PPA design goals.

The Calibre RealTime Digital interface provides direct calls to Calibre analysis engines running foundry-qualified signoff Calibre rule decks during digital design flows. These engines perform fast, incremental checking near shapes being edited, providing nearly instantaneous feedback on DRC violations. This feedback in the P&R domain enables MaxLinear engineers to quickly implement and check correct-by-construction fixes without the need for full DRC iterations. And, because the full range of Calibre physical verification functionality is available, they can interactively explore the cause of a DRC error and perform what-if analysis to determine the optimum fix.

Adopting the Calibre RealTime Digital interface enabled MaxLinear designers to accelerate their DRC closure and save weeks in their tapeout schedules for all designs at all nodes. If you’d like to see the details of how MaxLinear used the Calibre RealTime Digital interface, and learn how you can achieve similar results, download a copy of our white paper, MaxLinear and Calibre RealTime Digital: Faster signoff DRC plus optimization for manufacturability.