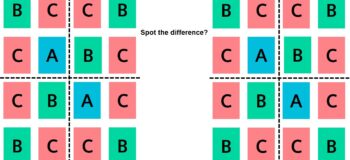

Reliability checking for memory circuit design doesn’t have to destroy your eyesight!

By Hossam Sarhan

Memory blocks contain sensitive analog circuits that are crucial for the proper functionality of the whole design. but reliability verification has always been a challenge for memory designs. Validating the reliability of your design against layout-dependent effects and manufacturing variations is critical. However, with advances in technology and the increasing complexity of layouts, traditional visual inspection is no longer the answer. At least not if you want to get to market on schedule…and save your eyesight in the process.

You also know as well as anyone that some of those effects won’t show up until the chip is in silicon, but there’s only so much time in the day, and you’re careful to use best design practices to avoid (or at least minimize) the impact of layout-dependent effects and manufacturing variation. Right? But no design is perfect, and catching reliability layout issues is better done while it’s still just a design, rather than finding out that your entire wafer run is defective. Ouch…

The Calibre PERC reliability platform provides comprehensive and easy-to-use automated reliability verification for your design, regardless of technology or design complexity. Using Calibre PERC packaged checks, you can quickly and easily combine multiple pre-coded checks targeting layout verification issues such as symmetry (including common centroid), device matching, alignment, and other layout reliability checks, in addition to topological checks for validating the devices used in your design.

Want to learn more about these pre-coded reliability checks, and see how you could be using them to more quickly verify and optimize your memory designs? Download our white paper, Comprehensive layout reliability verification for memory design, and give it a read.

Oh, and…second row, device B.