Plug and Play ESD protection

By Mark Tawfik

Electrostatic discharge (ESD) is the discharge of static electrical current when two objects come into contact. One of the most powerful and obvious examples of an ESD event is a lightning strike. While it’s unlikely that lightning will ever be an issue for most integrated circuits (ICs), electronic devices are vulnerable to damage caused by even low voltage ESD events. For this reason, IC design companies include ESD protection circuits in the device designs. However, to ensure that these protection circuits work as intended, designers must verify their construction against design rules that define the proper construction and placement of these circuits.

Even for experts, electronic design automation (EDA) verification of electrostatic discharge (ESD) protection can be a challenging and complex task. Different integrated circuit (IC) design companies use different ESD protection approaches, different design flows, and different verification tools. Failure to find and eliminate ESD susceptibilities may cost a company a lot, in both money and reputation, if a vulnerable chip makes it through manufacturing and is released into the market.

The ESD Association (ESDA) is a voluntary professional association dedicated to advancing the understanding of the theory and practice of ESD avoidance. To establish a consistent and comprehensive ESD EDA verification flow, the ESD Association (ESDA) provides a list of important ESD design rules and corresponding compliance checks to help IC design teams protect their designs against ESD events. These checks encompass a combination of very complex geometric and topological data that can make them challenging to set up and run accurately.

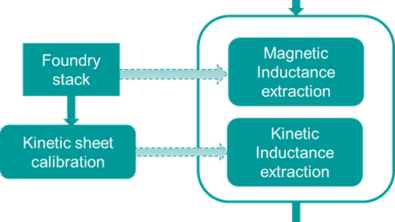

The Calibre PERC reliability platform performs a wide range of complex design reliability checks, using both foundry design rules and a design team’s custom rules. Designers can embed Calibre PERC reliability checks into their existing design flows as part of an integrated Calibre platform for cell and full-chip verification. Bringing together rules coded in both the standard verification rule format (SVRF) and the Tcl-based verification format (TVF) language across all applications provides designers with the flexibility and adaptability required to meet the particular and advancing needs of their design teams, while guaranteeing compatibility with all foundries.

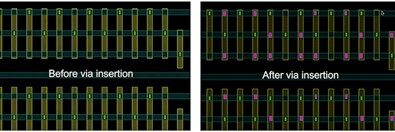

To simplify and standardize ESD protection verification, the Calibre PERC platform provides pre-coded packaged checks for each of the four ESDA check categories (protected circuit, cell level, intra-power domain, and inter-power domain). Designers can run these checks using the default parameters or by applying desired modifications, eliminating the need for manually coded checks. Not only do these packaged checks ensure compliance with the ESDA design rules on all ESD design levels from device to full chip level, but they also save design companies the time and resources needed to code and maintain their own checks.

Designers can run any combination of Calibre PERC packaged ESD checks, then analyze and debug the results using the Calibre RVE results viewer.

If you’d like to learn more, we have a technical paper available that has all the details: Ensuring ESD protection verification with Calibre PERC packaged checks. Why not download your copy and discover how your company can get fast, accurate ESD verification while reducing time to market (and engineer stress)?