Struggling to verify the reliability of your multiple-power-domain designs?

By Hossam Sarhan

With the growing complexity of system-on-chip designs and technology scaling, multiple power domains are needed to optimize both performance and power consumption of the chip. Communication between these different power domains is crucial, making reliability verification essential for such designs. However, creating the correct set of reliability checks for these designs can be time-consuming, and tricky to get right.

The reliability challenges facing engineers in multiple power domain designs include:

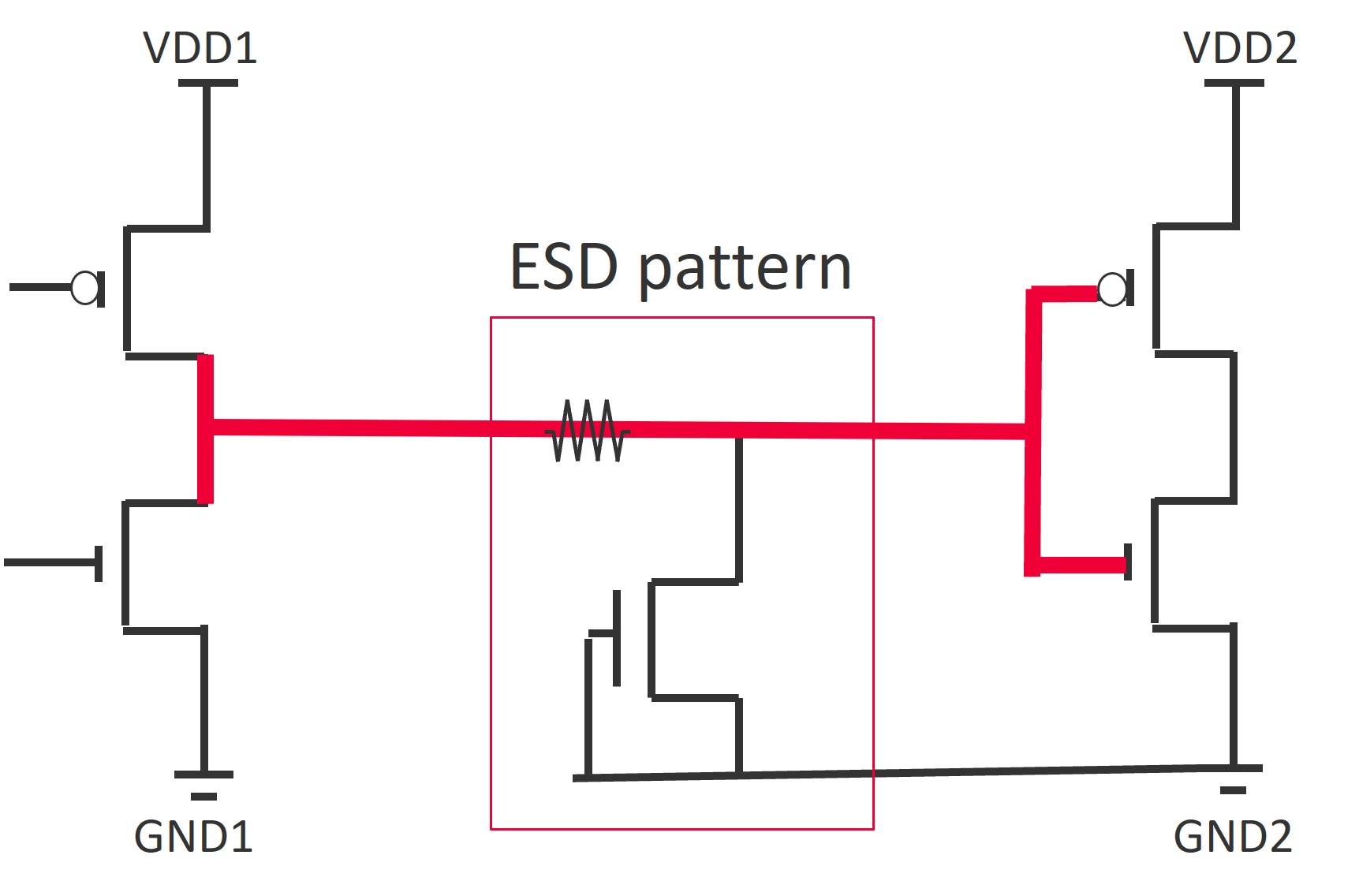

- validation that voltage differences across a device remain within an acceptable value to avoid electrical overstress (EOS) conditions

- verification that the right level shifters are installed to safely manage communications between different voltage domains

- detection of cross-power-domain configurations with the proper ESD protection

With all these challenges to design performance and reliability, engineers need all the support they can get! Using a minimum setup, designers can easily use the Calibre PERC packaged checks flow to select and combine EOS, level-shifter detection, and cross-power-domain checks for their multiple power domain designs without worrying about coding complex checks. Using the Calibre PERC packaged checks flow with pre-coded checks helps design teams shorten the design verification cycle for designs with multiple power domains, while safeguarding product reliability.

Want to learn more about these multiple-power domain Calibre PERC packaged checks, and see how you could be using them to quickly verify and optimize your designs? Download our technical paper Complete reliability verification for multiple power domain designs, and give it a read.