Fast, efficient, productive? Your early-stage IC design physical verification can be all that…

By John Ferguson and Nermeen Hossam

With each new process node comes more complex requirements needed to ensure working silicon. In the world of integrated circuit (IC) physical verification, this growth in requirements translates to more checks to run, more errors to parse through, more edits to correct errors, more iterations to achieve clean designs, and longer runtimes per iteration. As part of Siemens’s continuous efforts to help design companies bring novel chip designs to market as fast as possible, the Calibre Design Solutions division has implemented multiple features to support a shift-left strategy to help design teams address these challenges and reduce time to tapeout.

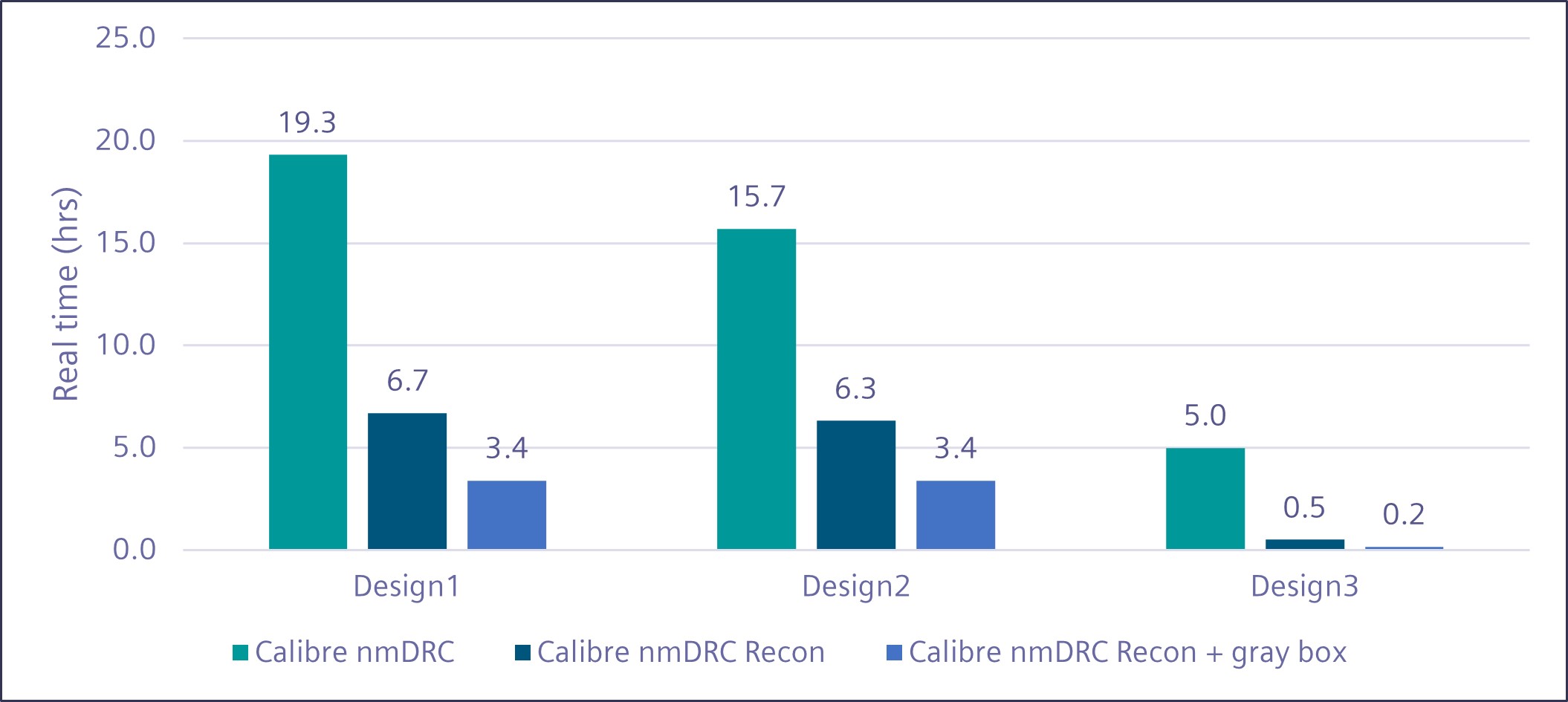

While there are many tools and functionalities employed in a shift-left strategy, our recent paper, Speed up early design rule exploration & physical verification, examines how the Calibre nmDRC Recon and Calibre Auto-Waivers tools can help design companies speed up and improve early-stage design verification. The Calibre nmDRC Recon tool allows design teams to run a selected set of Calibre signoff design rule checks (DRC) to help reduce runtimes for early/incomplete design data by focusing on identifying critical early-stage systemic design errors. During error debugging, the Calibre Auto-Waivers tool uses several key new capabilities to not just to eliminate false errors, but also give design teams more information about the real errors to help designers make fast, accurate decisions on fix strategies. Both of these capabilities have been adopted extensively at many of the world’s leading IC design companies, providing designers with the ability to quickly identify not just the individual DRC errors, but also the fundamental design flaws responsible. In combination, these tools and capabilities can drive significant reductions in total time and manual effort required to go from early/incomplete design to tapeout-ready.

Want to learn more? To get an in-depth look at how your design team can employ these shift-left strategies to run more efficient and productive early-stage IC design verification, download a copy of our paper today!