Help! I’m not an ESD expert! Reducing ESD verification complexity

By Abdellah Bakhali

If you’re not an electrostatic discharge (ESD) expert (and let’s face it, most of us aren’t), verifying reliability requirements like ESD can be challenging. ESD checks usually require a combination of geometric and topological data, including the identification of possible areas of electrical failure, geometrical constraints of device dimensions, the number of device fingers, distance from supply pads, and different circuitry requirements for multiple power domains. Get any of those wrong, and when that chip goes to manufacturing and out into the market, your company can be in for a world of hurt!

Cell-based reliability verification

The Calibre® PERC™ reliability platform offers pre-coded, cell-based, logic-driven layout (LDL) packaged checks that engineers can use to assess the ESD robustness of a layout, even if they don’t have extensive ESD proficiency. But wait, what does LDL mean? The LDL technology built into the Calibre PERC platform enables the tool to automatically combine geometric and topological data in a single check. That combination is required for many reliability checks that are driven by interdependent constraints, such as current density checks, where the allowable current value is dependent on the interconnect width measurement and resistance extraction.

Okay, then, what do you mean by cell-based? When an LDL cell-based check is executed, device extraction is disabled, and all pins not connected to devices and all empty sub-circuits are preserved in the extracted layout netlist for topological analysis. That makes it easier to check connectivity to any desired cell port (where the cell acts as a hierarchical cell). Because device extraction isn’t required for an LDL cell-based check, you don’t need an LVS-clean layout with devices present to run LDL checks on cell placements. Also, because the device modules are skipped during circuit extraction, cell-based checks generally run very quickly.

Cell-based ESD verification

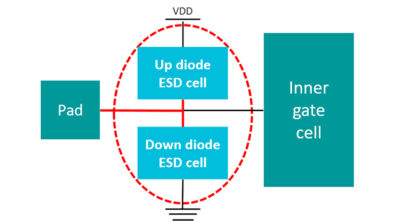

What does that all mean to you? Now, instead of having to create a complex topology definition, you can detect ESD devices just using cell names! ESD cells are typically well-identified in a design, because the cell name contains very specific keywords like “ESD” or “CLAMP”. You only need the cell name and port names to define a new ESD cell that can be used with all ESD checks, which makes it easy for designers to quickly and accurately identify and evaluate ESD structures using a Calibre PERC cell-based ESD check. Since any cell can be used and defined as an ESD device, designers can work with a bottom-up approach. Once a macro block is fully validated for ESD, they can define the block as a new ESD cell to check the top-level connectivity.

Cell-based P2P and CD checks

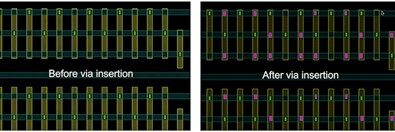

Point-to-point (P2P) parasitic resistance and current density (CD) checks are two types of checks that are essential to comprehensive ESD verification. In an ESD protection circuit, clamps are the devices used to provide the discharge path for an ESD event that happens between any pad and port. Clamps include not only power clamps, but also all the other ESD protection that will form the ESD network. Their ability to manage the excess current in an ESD event can be affected by parasitic resistance and current density. The Calibre PERC cell-based P2P/CD packaged check can run complex P2P and CD full-path checks using very simple and flexible XML rules that cover three check types: pin to clamp, clamp to clamp, and pin to pin. These pre-coded packaged checks enable designers with any level of familiarity in Calibre PERC usage to build a variety of P2P resistance and CD checks for ESD validation.

If you’d like to learn more, we have a technical paper available that has all the details: Evaluate ESD robustness with cell-based P2P/CD verification. Why not download a copy to find out how your company can get fast, accurate reliability verification while reducing time to market (and engineer stress)?