Streamlining IC design verification with Calibre nmLVS Recon

By Kesmat Shahin

As integrated circuits (ICs) become more complex, meeting tapeout schedules has become increasingly challenging. Statistics from industry conference surveys reveal that a shocking 50% or so of scheduled tapeouts slip each year. While multiple factors contribute to missed tapeouts, one critical component is the extensive time required for the signoff layout verification cycle. This prolonged duration significantly affects the overall signoff process, with much of the impact attributed to node-over-node complexity. This complexity stems from various factors such as increased design complexity, the proliferation of devices and polygons, introduction of new device types, and the need for more intricate measurements and parameter calculations. As IC circuit verification rules become more intricate, design companies face substantial growth in circuit verification operations from one node to the next.

So let’s explore how the Calibre® nmLVS Recon™ tool addresses these challenges! With a focus on early stage layout vs. schematic (LVS) and circuit verification, we can delve into its capabilities in enhancing the verification and debugging processes, ultimately streamlining IC design verification and reducing time to market.

The challenge of early stage design verification

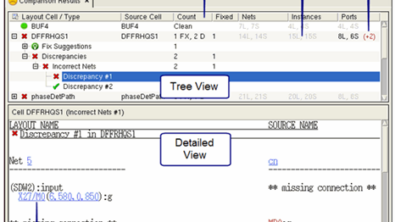

As IC designs grow in complexity, early stage LVS verification and debugging become increasingly critical. Incomplete or “dirty” design layouts often result in a multitude of connectivity errors, causing bottlenecks not only for LVS, but also for other essential physical verification flows. These flows include reliability checks, voltage-dependent design rule checking (DRC), and via/fill insertion, all of which rely on accurate connectivity for valid results. Debugging these errors necessitates numerous iterations, potentially leading to thousands or even millions of errors, further complicating the process.

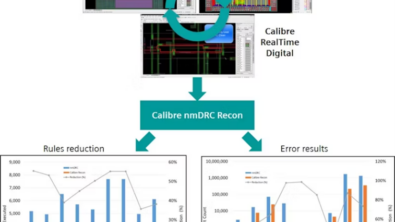

The solution: Calibre® nmLVS Recon™ targeted design stage verification

The Calibre® nmLVS Recon™ tool emerges as a groundbreaking solution, specifically designed to improve early LVS verification and debugging flows, reducing overall IC design verification and debugging time.

Targeted early stage circuit verification

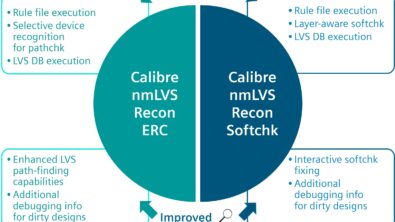

Calibre nmLVS Recon targeted verification focuses on addressing early design stage circuit verification pain points, such as short isolation (SI), electrical rule checking (ERC), and soft connection checking (softchk). This targeted approach empowers designers to perform efficient and focused early stage LVS runs, streamlining their workflow.

Early design stage ERC & soft connection checking

Debugging ERC or softchk issues in the early design stages using a signoff LVS flow can be cumbersome and time-consuming. Calibre nmLVS Recon focused solutions expedite these processes:

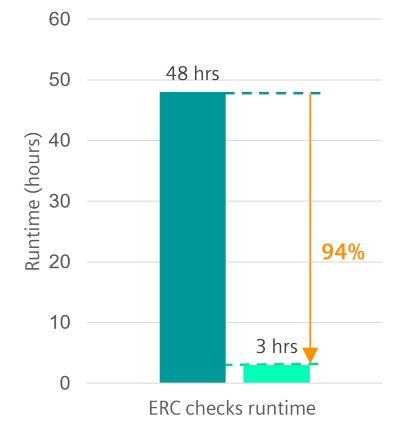

1. Rule file execution with selective device for path checking (pathchk) Running ERC as part of a full signoff run can lead to extended runtimes. Calibre nmLVS Recon path-based checking allows designers to run focused ERC quickly, reducing turnaround time by focusing only on essential areas. This selective device recognition can also enhance data partitioning among different groups, further improving performance.

2. Database re-use The tool enables designers to run ERC checks using previously-generated LVS databases, saving time and resources. Incremental runs on existing databases eliminate redundant steps, contributing to significant time savings.

3. Enhanced LVS path-finding capability & debugging Calibre nmLVS Recon ERC functionality streamlines debugging by providing designers with comprehensive information about the path, eliminating the need for multiple manual steps, and making it easier to pinpoint and fix ERC violations.

Streamlining softchk verification

Calibre nmLVS Recon features enable designers to streamline soft connection checking:

1. Rule file execution with layer-aware Calibre nmLVS Recon softchk The tool allows designers to focus only on the layers involved in softchk issues, saving time and memory. Layer grouping further enhances efficiency, enabling parallel checking.

2. Database re-use Similar to ERC, designers can run softchk using previously-generated LVS databases, reducing runtimes and enabling quicker iterations.

3. Interactive softchk fixing with additional debugging information Calibre nmLVS Recon Softchk provides interactive debugging capabilities and immediate visual fix confirmation, simplifying the debugging process and reducing overall debug time.

We offer a deep dive into this topic in our technical paper: Achieve dramatic productivity and turnaround time improvements in early design electrical rule checking

Conclusion

Calibre nmLVS Recon focused verification transforms the landscape of early-design stage IC design verification. By targeting relevant early design stage circuit issues and streamlining the verification and debugging processes, designers can find and fix critical design issues quickly and efficiently. This tool facilitates a “shift left” approach in circuit verification, enabling design and verification engineers to navigate early-design stage circuit verification faster and with fewer iterations. Ultimately, this targeted early-design stage verification leads to a reduction in delivery schedules and time to market, making the Calibre nmLVS Recon tool a vital and valuable asset in IC design verification.