Searching for Latch-up in All the Right Places

By Matthew Hogan – Mentor, A Siemens Business

While any error in a layout could be deemed unintentional (I mean, who makes mistakes on purpose??), some errors are more unintentional than others.

Latch-up, or LUP, is the inadvertent creation of parasitic PNP and NPN junctions in a circuit that can cause permanent damage that either impacts the chip’s performance or contributes to a fatal chip failure. Not good.

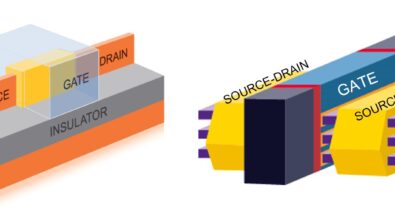

Of course, LUP isn’t exactly something new, but three factors are bringing it to the forefront of circuit verification. First, tighter design margins are leaving little room for those critical distances that reduce susceptibility to LUP conditions. Second, the design rule checks (DRC) used to find potential LUP-sensitive geometric elements are no longer sufficient, because they can’t account for the influence of voltage on these spacing requirements. Third, with the number of power domains increasing in today’s designs, the complexity of the protection required is also increasing. Not only do you have to recognize all the different voltages, but you need to understand how the domains switch, and which parts of the design are active at any given time.

New reliability rule decks have been created that take advantage of innovative automated verification capabilities in tools like the Calibre® PERC™ reliability platform. With its ability to consider both netlist and layout (GDS) information simultaneously, the Calibre PERC reliability verification platform can perform complex electrical checks that require both layout-related parameters and circuitry-dependent checks, such as voltage-aware net checking. With this functionality, the Calibre PERC platform is uniquely able to detect net connectivity through current conduction devices, enabling it to identify LUP risks that would be missed with traditional DRC.

In addition, many of these rule decks enable design teams to run reliability checks not only at the full-chip level, but also at the intellectual property (IP) block level. This incremental approach helps provide context for problematic areas, particularly for IPs that are being used in a different context from previous implementations, or whose geometries have been shrunk to accommodate a new process node. Eliminating LUP conditions during the design phase can provide your company with market advantage in both time-to-market and product lifecycle performance.

If you’d like to learn more about automated LUP checking, or the Calibre PERC reliability platform, check out our white paper, Automated and Context-Aware Latch-Up checking with the Calibre PERC Reliability Platform