Get to yield ramp faster…even with new design styles

By Wael Manhawy and Joe Kwan – Mentor, A Siemens Business

Having trouble ramping yield for new, unproven design styles? Experiments with an innovative new test process proved it can find yield limiters early on in technology development….

Predicting and improving the yield in the early stages of technology development is one of the main reasons for creating test macros on test masks. Identifying potential manufacturing failures and design flaws as early as possible lets design teams develop corrective actions and/or process changes that reduce the time it takes to ramp to the desired yield in production.

However, when you’re implementing a new design style that has no relevant production history, like a self-aligned multi-patterning (SAMP) layout, it’s hard to design accurate test structures. There’s no prior test data or existing knowledge bank that designers can draw from to create useful macros. Looks like a long, hard slog, right?

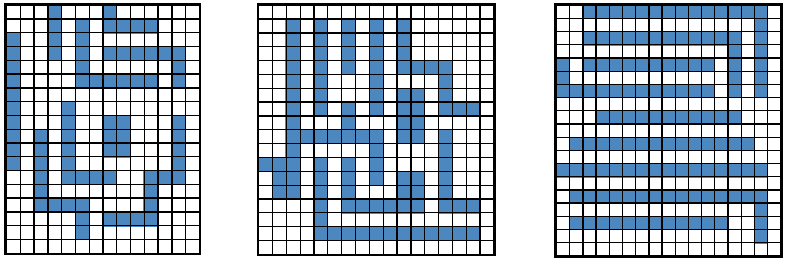

Not necessarily. At Mentor, we’ve created an innovative new technology that lets designers generate layout clips that look like realistic designs for any design style, even one that’s never been produced before. These layout clips can then be added to the design of experiment (DoE) to predict yield. The key component of our solution is the Calibre® LSG layout schema generator, which generates random, realistic design-like layouts without design rule violations. This tool uses a Monte Carlo method to apply randomness in the generation of layout clips by inserting basic unit patterns in a grid. These unit patterns represent simple rectangular and square polygons, as well as a unit pattern for inserting spaces in the design. Unit pattern sizes depend on the technology pitch value. During the generation of the layouts, known design rules are applied as constraints for unit pattern insertion. Once the rules are configured, an arbitrary size of layout clips can be generated. These generated patterns can then be added to the typical contents of regular test patterns. Circuitry can also be added to the generated clips to make them electrically measurable for the detection of potential failures.

To demonstrate how it works and the effectiveness of the solution, we created test patterns for a SAMP design, and used them in two experiments—one to collect data about random defects caused by conducting particles, and the second to detect systematic cut mask resolution problems. Results from the first test were used to model the defect density and estimate the yield target, while the repetitive fail data from the second test enabled the identification of a poorly resolving cut shape.

Of course, the LSG solution isn’t limited to SAMP designs. It can be applied to virtually any design style and technology node. Want to know more about the specifics? Download a copy of our white paper, Improving yield for new design styles during technology development.