Stronger, better, earlier latch-up protection? Yes, please!

By Flint Yoder – Mentor, A Siemens Business

Tight schedules? Worried about product reliability? Now you can find and eliminate latch-up sensitivity during schematic design, and avoid those post-layout nightmares.

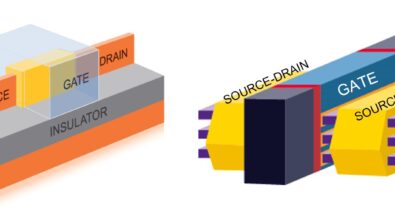

Latch-up…the bane of circuit designers and circuit verification engineers. What is latch-up? It occurs when an unintentional structure forms from parasitic elements in an IC, and then becomes locked, or latched, into an on state. Latched parasitic elements will continue to feed themselves such that they remain in an on state, which alters the intended behavior of the circuit. Effects can range from loss of functionality to permanent damage. No wonder designers do everything they can to avoid creating design conditions that allow latch-up to occur!

However, the unpredictable and unintentional nature of a latch-up event is precisely what makes it difficult to detect latch-up susceptibility during design and verification. It isn’t caused directly by the circuit connectivity, but is instead interrelated to both the circuitry and the physical layout. IP blocks present a particular challenge, because each block might be inert by itself, but have an adverse reaction when placed near another IP block.

Traditional detection and prevention methods include using spacing (to increase the amount of current required to latch the parasitic device) and guard rings (supply-tied metal that collects enough of the substrate current to prevent latching). However, both of these methods require a high degree of layout completion to be effective, and as we all know, late-stage changes are difficult and expensive.

By examining schematic data instead, well before layout, designers can identify latch-up sensitive structures at a point where their susceptibility can actually influence how the design is put together. There are several scenarios that can be identified using topological checks that identify high latch-up susceptibility. Finding these scenarios during early design stages makes it possible to actively remove or mitigate them before any layout routing is completed.

The Calibre® PERC™ reliability platform provides a robust and efficient topological analysis engine that designers can use to automatically identify nets and devices of latch-up interest on any design, both for schematic netlists and layout databases. By running Calibre PERC verification on the schematic netlist during early design phases, designers can quickly identify latch-up sensitive scenarios through topological analysis. Calibre PERC verification can then be run again during the post-layout stage to ensure the full chip is protected against performance degradation and product failure.

To learn more about latch-up detection and prevention, download a copy of our white paper, Robust latch-up protection with schematic netlist circuit verification