Want a better, faster way to write reliability rules and checks? Try an XML constraint file!

By Dina Medhat – Mentor, A Siemens Business

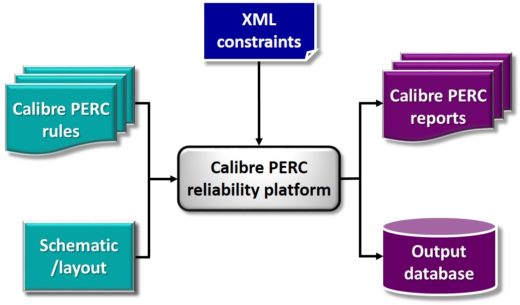

XML constraint files are the better, faster way to define Calibre PERC reliability rules and checks. And you can combine multiple IP constraint files with one chip-level file for complete, accurate chip verification.

Writing rules and checks to evaluate reliability conditions in integrated circuit (IC) layouts can be time-consuming and frustrating. You have to know the rule syntax, and you essentially end up creating the same rules and checks (with minor variations) for multiple designs and technology nodes. Try to save a little time by copying and modifying existing rules, and all of a sudden you’ve got inconsistency and unexpected errors in your check results.

What if I told you there’s a better, faster, easier way that ensures uniform rule and check definitions? Well, lucky for you, now there is. Rule developers can create XML constraint files (using basic XML syntax) to define Calibre™ PERC™ reliability rule constraints and their associated parameters. Designers can then simply fill in the appropriate parameter values when developing their reliability checks, without having to know rule syntax or risk mangling the rule deck. Separate XML files can be created for each type of check or check set, making maintenance and edits easy and fast. Designers can then mix and match these XML files during checking runs, which means no more copying files for reuse. This ability to include more than one XML file in a checking run also means designers can easily reference XML files created for various IP when running reliability checking at the chip-level.

What if I told you there’s a better, faster, easier way that ensures uniform rule and check definitions? Well, lucky for you, now there is. Rule developers can create XML constraint files (using basic XML syntax) to define Calibre™ PERC™ reliability rule constraints and their associated parameters. Designers can then simply fill in the appropriate parameter values when developing their reliability checks, without having to know rule syntax or risk mangling the rule deck. Separate XML files can be created for each type of check or check set, making maintenance and edits easy and fast. Designers can then mix and match these XML files during checking runs, which means no more copying files for reuse. This ability to include more than one XML file in a checking run also means designers can easily reference XML files created for various IP when running reliability checking at the chip-level.

These XML constraint files can be created for all Calibre PERC topological/voltage and geometrical checks. Want to see actual code examples for various types of reliability checks? Check out our white paper, XML constraint files: A better way to write reliability rules and checks, to get started.