Turn IC verification challenge from a hard slog into a walk in the park by using static checks

By Neel Natekar

As integrated circuits (ICs) grow in complexity, they create new challenges for IC verification flows and electronic design automation (EDA) verification tools. In electrical verification, running dynamic simulations and applying manual verification techniques is simply too slow and unwieldy for most design schedules, and often doesn’t even provide full coverage. Is there an alternative? Yes! Automated configurable static checks can not only ensure the desired connectivity is in place, but also identify structural issues in the design, all with minimum manual intervention.

These fully programmable and easily configurable checks provide a verification solution that is deterministic, not to mention lightning fast. One such area where these checks are especially useful is power intent verification. As the number of power domains on a chip increase, the potential electrical stress on devices also increases, as does the stress level of the reliability verification team, worried about missing a level shifter cell on a voltage domain crossing. Catching such structural issues is essential to avoiding issues such as excessive power draw, reduced performance, or non-functional intellectual property (IP).

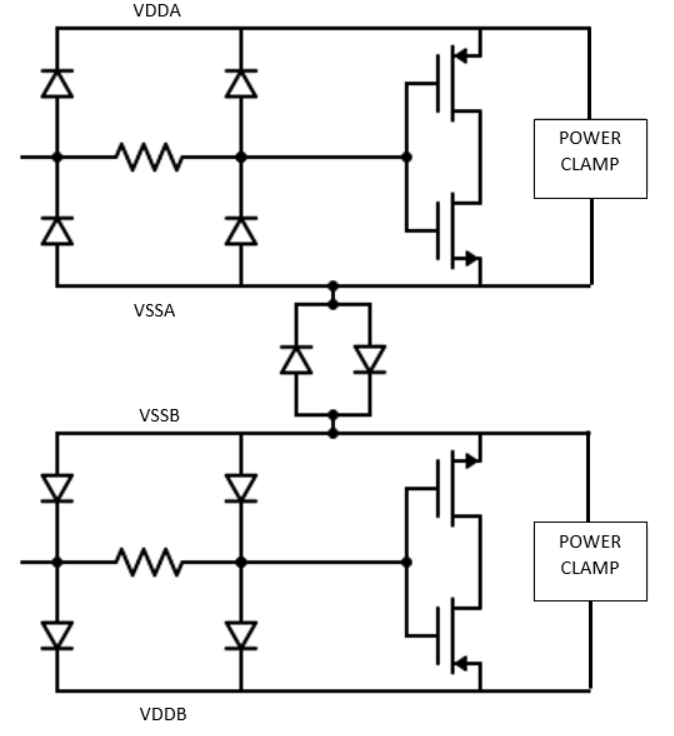

Electrostatic discharge (ESD) verification is also a massive challenge, as the distribution of the ESD protection elements across multiple levels of hierarchy and different parts of IC and the growing dominance of the parasitic resistances increases the complexity of the process. Simply running simulations at the IP level or using approximations for parasitics is highly risky, and a perfect recipe for ESD failures. Automated static ESD checks, on the other hand, can be run at the full-chip level, bypassing the risks associated with these approximations or in performing sign-off analysis merely at IP level.

Even better, programmable static checking is not just limited to schematic and pre-layout netlist checking, but can also be used for layout verification. It is becoming increasingly important to analyze the layout-dependent effects in the IC, beyond what can be validated by traditional design rule checking (DRC). Using sophisticated context-aware checks, designers can quickly and accurately check for subtle errors such as mismatched or asymmetrical geometries, voltage-dependent spacing, etc.

If you’re interested in learning more about using automated static checks to not only reduce the time and effort used to verify your designs, but also improve your results, download a copy of our technical paper, Improve circuit performance and reliability with automated static check verification. Maybe instead of that hard, painful workout you’re used to, you can start enjoying more pleasant walks in the park!