Stronger together! Context-aware SPICE simulation combines the strengths of static and dynamic verification for faster, more precise full-chip ESD verification

By Neel Natekar

Running dynamic simulations for full-chip ESD verification of ICs has become increasingly difficult (and in some cases, practically impossible), due to the complexity of designs and explosion in the transistor count. As a result, designers often resort to shortcuts, such as running simulations at the block or IP level or using manual techniques to approximate parasitics at higher levels and set up testbenches to model or mimic ESD discharge paths at the full-chip level. However, these techniques are not optimal and, in some cases, can even be risky, due to their various limitations. For example, it is easy to miss the resistance on some paths or enter incorrect values when manually setting up testbenches. Then there’s the snapback behavior of ESD elements, which can cause convergence issues in traditional SPICE simulators. Even worse, it can take days to get results (if any) from these runs, wasting valuable time and resources.

Many designers use static point to point (P2P) resistance checks in an effort to avoid these issues. This approach helps them achieve ESD signoff on their designs with foundry-certified checks and resistance limits. The static P2P technique provides greatly improved capacity and runtimes compared to a traditional SPICE simulation, making it possible to run ESD checks at the full-chip level with a reasonable turnaround time. Problem solved? Not quite…

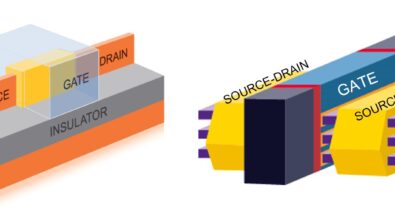

When designers are trying to optimize for metrics such as maximum performance and low signal-to-noise ratios, they are challenged by the stringent limits set by the technology. It is crucial for them to understand the exact margins in the design, irrespective of whether checks are passing or failing these limits. Moreover, ESD protection devices have thousands of fingers, and the current distribution through them is non-uniform, so manually approximating resistance values for use in static checks can lead to a loss of fidelity.

When faced with these frustrating limitations, most designers wish they had a superpower that would let them run full-chip ESD verification quickly while still ensuring maximum design fidelity. The good news is—that superpower exists! Even better, while most superheroes must acquire their superpowers through some painful event, whether that’s being bitten by a spider or exposed to toxic levels of radiation, this superpower is readily available by combining the functionalities of the industry leading EDA tools you probably already have. Bet that’s a relief!

The innovative context-aware SPICE simulation flow combines the topology identification capability of the Calibre PERC engine with dynamic simulation through the Analog FastSPICE tool (the fastest nm circuit verification platform) to augment the P2P approach for full-chip ESD verification and signoff. This fully automated flow enables designers to know the exact design margins, while also understanding where and when any devices exceed their breakdown limits, without the need for any manual hacking or approximations.

We can’t promise you’ll suddenly be able to fly, or leap tall buildings in a single bound, but if you want to acquire this groundbreaking superpower that helps designers overcome shrinking design margins while improving the fidelity of results, download a copy of our technical paper, Context-aware SPICE simulation improves the fidelity of ESD analysis.