Save yourself the time—here’s a way for you to view native block instances from a full-chip context

By Ritu Walia

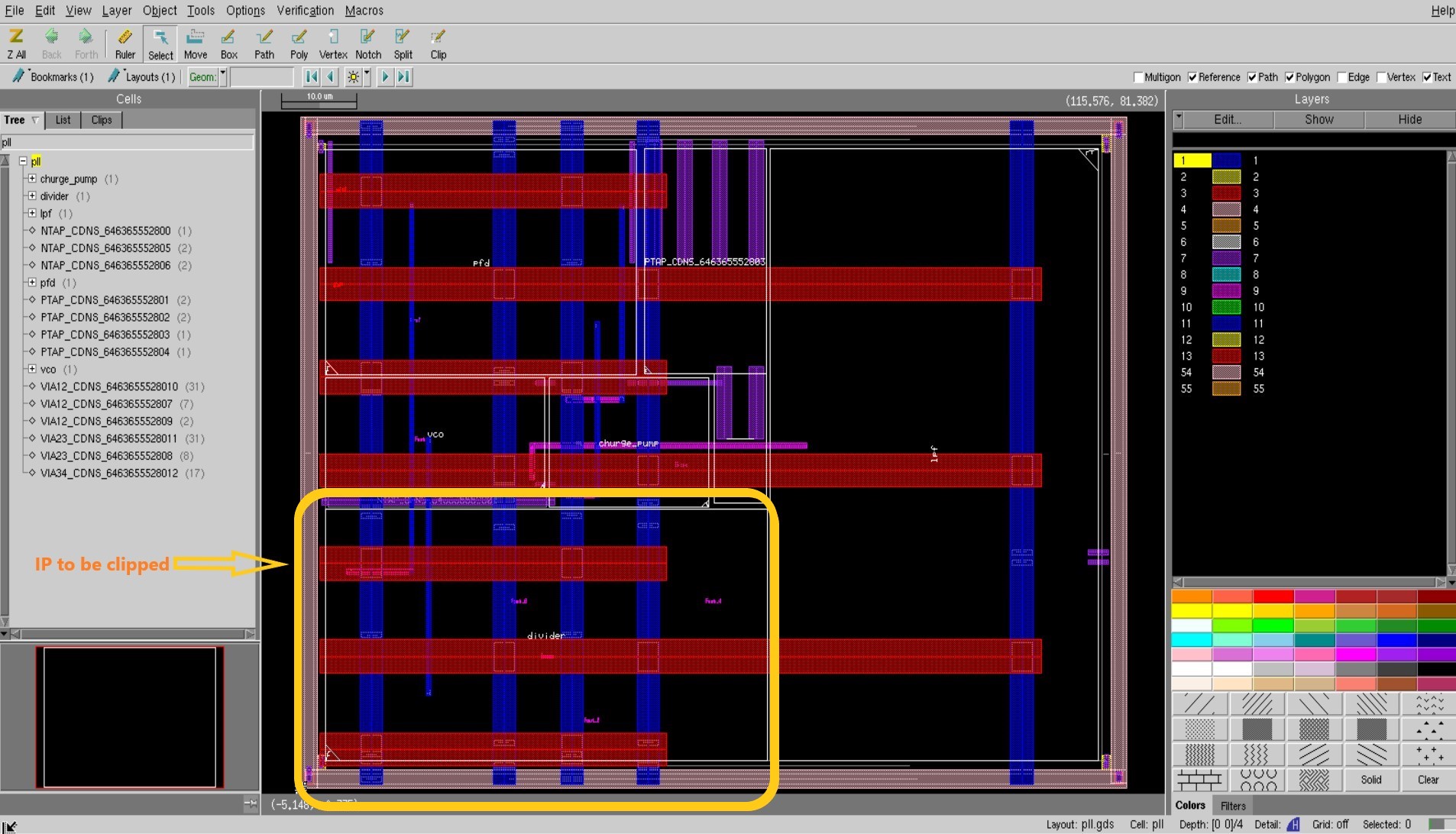

Imagine this: You primarily work on the design of a sub-block of an application-specific layout design, or perhaps an intellectual property (IP) block for a system-on-chip (SoC). You’ve designed your block, and it’s ready for the SoC team. As you work hand-in-hand with the team striving to deliver the SoC within the (forever) limited time-to-market window, you face a multitude of challenges—complex design rule checking (DRC), iterative debugging, combined with the need to ensure optimal performance of the full chip design that includes other blocks than yours—but now you have to view the design from a full-chip context. Wouldn’t it be nice if you could easily visualize all instances of your native IP block from a full-chip context during all that iterative rule checking and debugging?

You can! The Calibre® DESIGNrev™ tool provides a simple, yet effective, process for visualizing native IP blocks within the broader context of the complete chip layout. With those views, you can analyze and optimize your IP blocks more efficiently, reducing the time required for thorough debugging, and minimizing delays caused by iterative changes. The Calibre DESIGNrev clipping option lets you extract and visualize instances of your own IP blocks. Through a simple script, you can obtain boundary coordinates, create isolated clips, and generate an output layout containing only those IP references that you choose to view. Using the Calibre DESIGNrev clipping option can unlock the way to reducing time to tapeout while gaining more confidence in your block’s alignment with overall design specifications, smoothing the design flow and accelerating your chip design success!

For the full details, read or download a copy of our technical paper, Reduce time to tapeout with native IP block visualization in a full-chip context