Collaborative SoC Verification

By Matthew Hogan, Mentor Graphics

The increasing use of SoC designs turns efficient IC design and validation into a team sport.

With the widespread use of system-on-chip (SoC) designs, efficient integrated circuit (IC) design and validation is now a team sport. In many cases, long gone are the days where a single person was charged with responsibility for the entire design. Extensive intellectual property (IP) use, design re-use, and re-design from both internal and external sources have made successful IC design as much about efficient IP management and integration, as it is about creating new blocks and functionality.

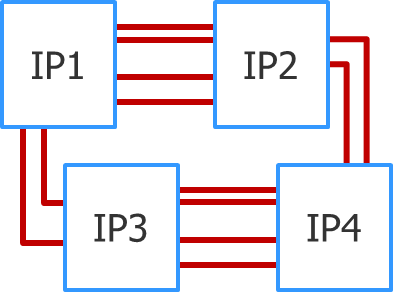

A lot of attention is paid to the top-level integration tasks of final assembly and full-chip verification, but these tasks happen towards the end of your IC design journey. While it is important to validate the correct interconnects and top-level assembly of each of your blocks in the design as a whole (Figure 1), how those blocks get there, bug-free and operationally correct, is an important aspect of meeting your design timelines.

Figure 1 – Multiple IP blocks comprise the top-level design, which must be validated as a whole.

Bottom-up design flows

Designing each IP block in isolation provides a great deal of autonomy, if isolation can actually be achieved. Issues such as interface definitions, as well as compliance to I/O switching and power consumption requirements, all pose challenges throughout the design flow. Validating individual IP blocks as you go, fixing each one as issues are found, provides a methodical and scalable workflow that accepts design growth and the addition of more functional blocks with relative ease. Understanding the context in which your IP will be used is an important aspect of the verification methodology that you employ. Interconnects must be robust, able to handle not only the internal voltage and currents that will be generated, but also to cope with the intended stresses of the final design assembly. On an IP block level that you control, this verification is probably a manageable task to ensure that your block either complies with the requirements and rule checks provided for validation, or that you have waiver documents in place for any outliers.

Top-down verification

Top-down full-chip verification is the most reliable methodology by far, when all the pieces are in place. However, that reliability comes at a cost. Waiting until all of the constituent IP blocks and elements are in place puts you towards the end of the project schedule. Time is short, schedules often slip, and final verification becomes a challenging and stressful period. Pulling in pre-verified IP blocks can limit the introduction of any newly-found violations to the integration process. How these blocks are connected, their implementation in the context of the larger design, and the application of previously created waivers can play a significant role in determining how challenging final verification is. A well thought-out verification flow can help immensely in the closing hours, but it’s not a one-person job when design issues are found, particularly those that span multiple IPs. The challenge is to effectively engage all team members, each with specific knowledge, in a collaborative manner across the whole chip.

Waiver flows need to be collaborative, too

Once “obvious” errors have been eliminated, the subtle job of understanding the interactions and nuances of the system being created falls to those who created it. Many times, a robust framework of IC validation checks can focus attention on those final few issues that will probably need specific IP knowledge to either waive or fix.

Many traditional waiver flows rely on a static model of verification results, and a single user wading through all results, for all IP blocks. While conceptually simple, this model creates a significant bottleneck in today’s large IP-based designs. With a high degree of IP re-use, the IP owner is best suited to validate the context of a flagged issue for that IP. The challenge, however, is to allow multiple IP owners to review, waive, and interact with the results for the entire design at the same time. Their efforts need to be collaborative and additive. Fighting for a “timeshare” on a design and asking others to stop working is not a productive solution. Moving forward, existing automated waiver management technology can and should be employed to support simultaneous waiver analysis and identification for multiple IP.

Conclusion

The ways we design and validate the complex interactions in designs with significant IP content have evolved over time to accommodate the changing requirements of such designs. However, waiver methodologies have lagged behind, creating potential bottlenecks. Validating IP blocks in isolation (including waiver annotation) as they are being designed can help, as can employing automated waiver management at different levels of design integration. Waiver flows that we have become accustomed to using for individual IP must evolve to accommodate multiple IP owners and the specific knowledge they hold for how these blocks are used in the context of larger SoC designs.

Author

Matthew Hogan is a Product Marketing Manager for Calibre Design Solutions at Mentor Graphics, with over 15 years of design and field experience.

Liked this article? Then try this –

Video: How to waive PERC results using Calibre RVE

This article was originally published on www.semimd.com