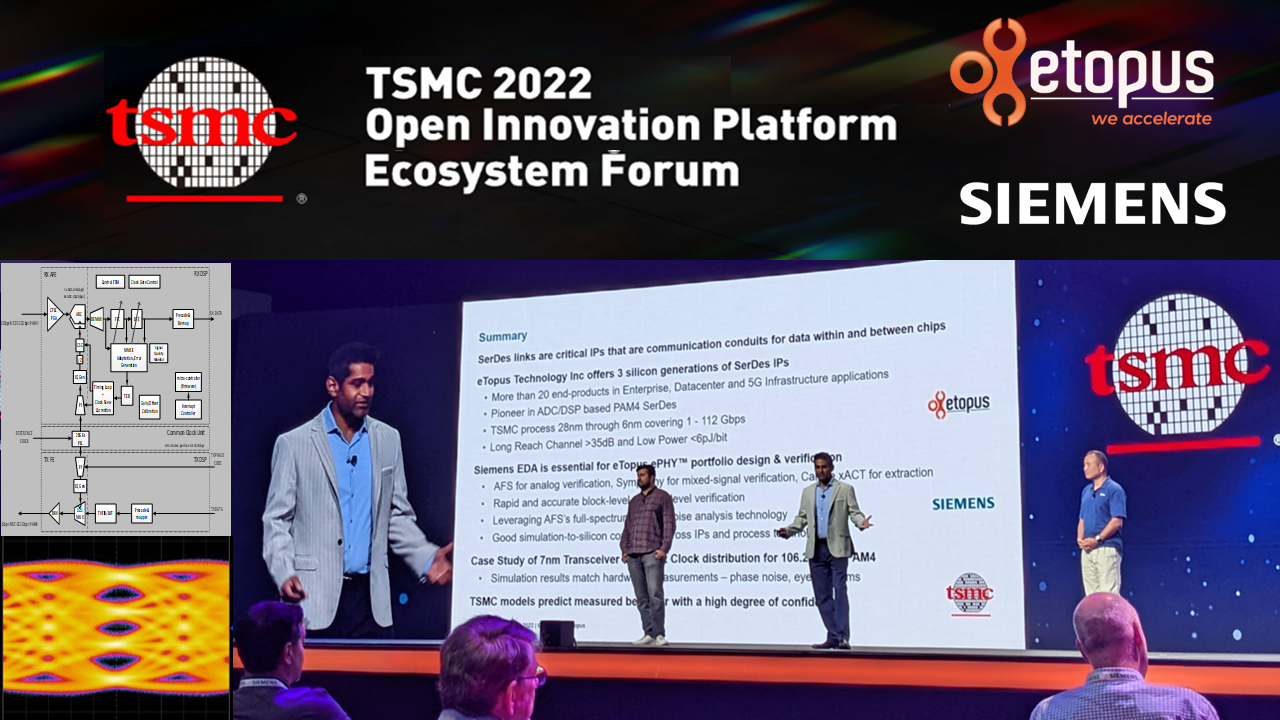

eTopus and Siemens partner on advanced transceivers taking mainstage at TSMC OIP 2022

Thanks to TSMC’s initiative and organization, their 2022 North America OIP (Open Innovation Platform) Ecosystem Forum at Santa Clara convention center on October 26th was buzzing with activity comparable to pre-pandemic levels with booths and presentations from semiconductor players around the ecosystem. The OIP presentation tracks on HPC & 3DIC, Mobile & Automotive, and IoT & RF were nothing less than spectacular with companies boasting their latest innovations, be it an IP, SoC, compute, memory or EDA provider. TSMC flexed on its own technology advancements and unveiled their TSMC 3DFabric™ Alliance on advanced packaging with partners in EDA, IP, DCA/VCA, Memory, OSAT, Substrate, Testing fronts.

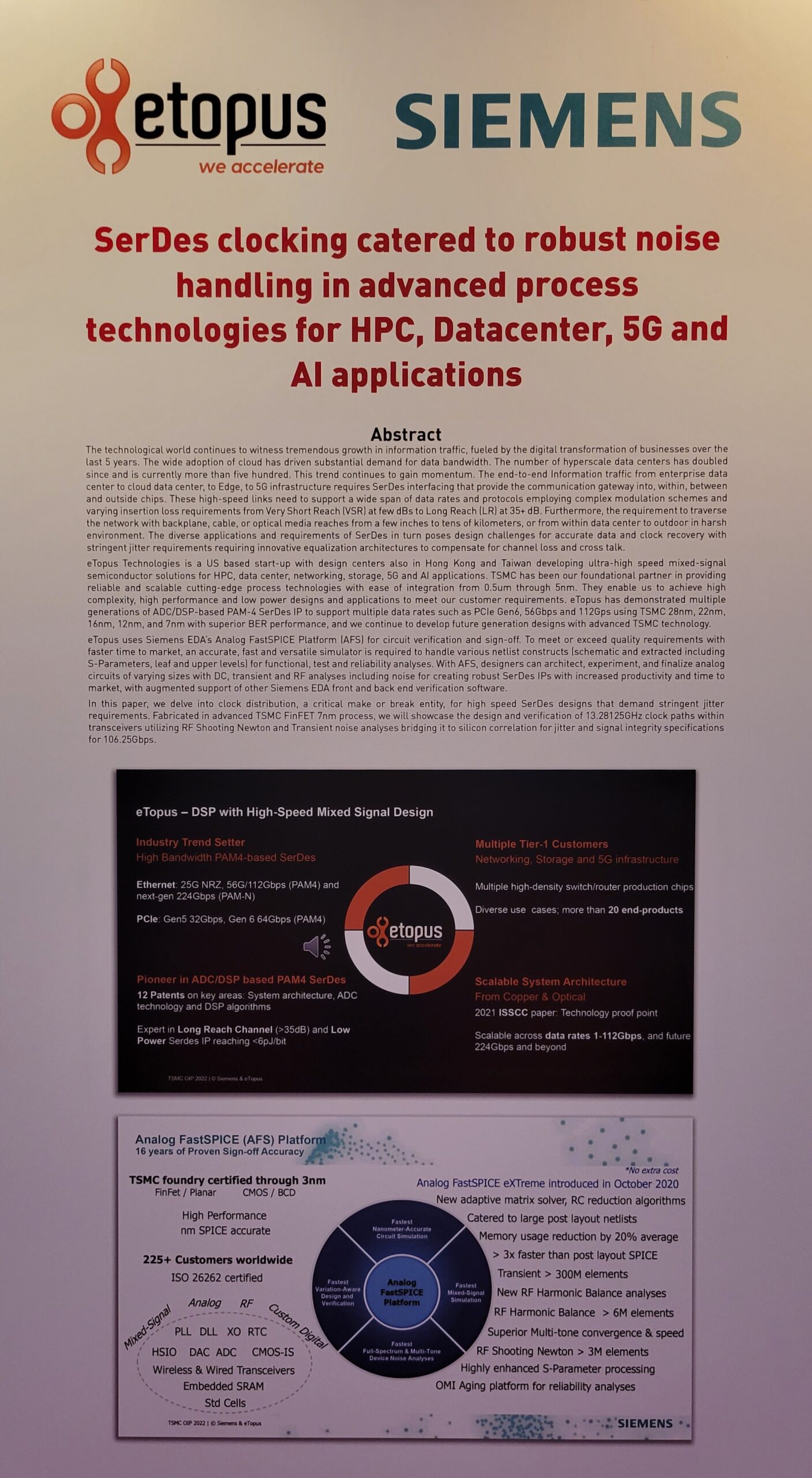

eTopus Technology Inc. is a US based start-up with design centers also in Hong Kong and Taiwan developing ultra-high speed mixed-signal semiconductor solutions for HPC, data center, networking, storage, 5G and AI applications. TSMC has been eTopus’s foundational partner in providing reliable and scalable cutting-edge process technologies with ease of integration from mature processes to advanced nodes. This has enabled eTopus to achieve highly complex, high performance and low power designs to meet their customer requirements and applications.

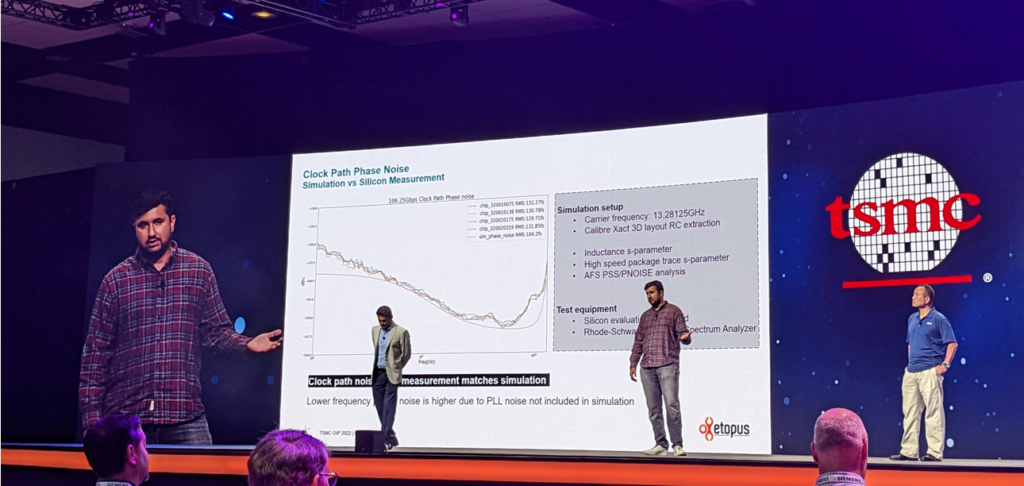

Siemens EDA is a trusted partner of eTopus enabling them for streamlined design and verification flows. eTopus utilize Siemens AMS verification and Calibre XACT extraction technologies in creating cutting-edge high speed serial links validated with utmost precision and silicon correlation in CMOS planar and FinFET process technologies. eTopus has demonstrated multiple generations of PAM-4 SerDes IP to support various data rates and protocol standards using TSMC 28nm, 22nm, 16nm, 12nm, and 7nm, and continues to develop next generation designs with advanced TSMC nodes.

Furthermore, Siemens is TSMC’s trusted EDA and Cloud partner committed to enabling and supporting TSMC technologies and our mutual clients with products that do not compromise on quality. Siemens EDA’s Analog FastSPICE (AFS) is a TSMC golden simulator, and AFS is qualified on all advanced nodes down to N3E with device and circuit qualifications, with continued collaboration in TMI support and TSMC reliability reference flows on advanced nodes.

We showcased our collaboration live in the HPC/3DIC track. eTopus ePHY SerDes offerings cover a wide span of data rates, protocol standards and insertion loss requirements from VSR at a few dB to LR at 35+ dN with complex modulation schemes. Their latest innovation is 112 Gbps ADC/DSP based PAM4 SerDes architectures, leading into next gen 224 Gbps PAM-N proto typing. Hence my branding and introduction of them at the presentation as “SoS” – SerDes on Steroids”! eTopus-Siemens Paper abstract HPC/3DIC Track

It has been my pleasure working with eTopus’s innovation team. Their speakers are Danfeng Xu (Co-founder and VP of Analog), Gary Kwan (Principal engineer) and Arnav Shah (Sr Staff engineer).

If you missed it live, you can register for the Online TSMC OIP event on November 10th, 2022. >> ONLINE event registration

Come embrace the innovation!

To learn more about Siemens AMS Verification technology, visit: Analog Mixed-Signal Verification | Siemens Software

To learn more about eTopus Technology Inc product portfolio, visit: https://www.etopus.com

Here are some snapshots from the event!