Diverse Ways To use Algorithms With Programmable Controllers in Tessent Memory BIST

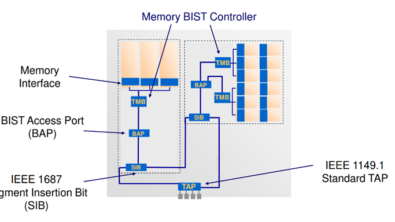

As part of the Tessent Memory BIST solution, Siemens provides a library of test patterns or algorithms for testing your memories. These algorithms represent some of the tests that you can perform on your memories using a Tessent Memory BIST Programmable controller.

To understand the spectrum of these algorithms better, we shall discuss the default algorithm, additional Tessent Library algorithms and custom algorithms (more commonly called user-defined algorithms).

The default algorithm is the algorithm the tool will see in and select from the memory library file. The file is received from the memory vendor and by default, the Tessent Memory BIST controller would only include whichever algorithm that is described in it. Depending on your testing needs, you might want to use another algorithm as the default algorithm however, and to do that, you can overwrite the algorithm in the configuration set up for Tessent Memory BIST hardware insertion. The default algorithm can either be a user-defined algorithm or one among the Tessent Library algorithms.

What if your testing needs require you to use more algorithms in addition to the default algorithm? In this case you could make use of the additional Tessent Library algorithms or custom / user-defined algorithms. The Tessent Library algorithms are provided in the Tessent Memory BIST library. You can point to these algorithms or use these algorithms in your memory core description files, and when you perform Memory BIST insertion, they will be inserted as well.

Like the Tessent Library algorithms, you can also additionally embed your own user-defined algorithms. You can do this with a soft-programmable controller or hard-programmable controller. With a soft-programmable controller, you are required to load the algorithm at TCK frequency, which could add to test time. This provides flexibility running additional algorithms, provided sufficient hardware instructions were allocated during insertion. Also, because the algorithm is loaded in at test time, seldom will you be 100% sure what size controller you are going to need so there is a risk you could use more flops (and thus, more area) than you need. In contrast, a hard-programmable controller is typically smaller (the flops take less area) and they start quicker, because you do not have to download the algorithm – but it does takes up silicon area. It will therefore come down to you as the user to decide whether using a soft-programmable controller or hard-programmable controller is better for your testing needs. That said, Tessent Memory BIST allows you to make slight modifications to the Memory BIST configuration to use either kind.

This link explains in further detail how to generate a soft-programmable controller. For more details and a step-by-step guide on how to use the default algorithm, Tessent Library algorithms and User Defined Algorithms, you can visit this link.

For Support and training information on Tessent Memory BIST and use of algorithms with Memory BIST, please refer to our Support Center and Siemens’ Xcelerator Academy Siemens’ Xcelerator Academy

Register to our upcoming EDA Expert Series Webinar!

By Jojo Walugembe

Associate Rotational Engineer – Tessent.

May 2024.