DDR – Increased Performance, Increased Design Challenges

If it weren’t for DDR SDRAM, many of today’s products would not be as feature-rich as they are, including servers, smartphones, computers, gaming consoles, and more. With each generation of DDR comes new advantages, such as increased speed and capacity and decreased power consumption, and also new challenges. Read our new white paper, The Design Advantages and Signal Integrity Challenges of DDR SDRAM.

DDR3 SDRAM brought improvements over DDR2, with bit rates that cover 800 Mb/s to 1600 Mb/s or more. It also increases bandwidth, lowers the operating voltage, and changes the driver impedance and on-die termination schemes. DDR3 uses “fly-by” topology, which means the Address/Command/Control and Clock are daisy-chained from one DRAM component to the next. This brings new signal-integrity design challenges, especially related to termination strategies, higher bit rates, and timing skew.

DDR3 SDRAM brought improvements over DDR2, with bit rates that cover 800 Mb/s to 1600 Mb/s or more. It also increases bandwidth, lowers the operating voltage, and changes the driver impedance and on-die termination schemes. DDR3 uses “fly-by” topology, which means the Address/Command/Control and Clock are daisy-chained from one DRAM component to the next. This brings new signal-integrity design challenges, especially related to termination strategies, higher bit rates, and timing skew.

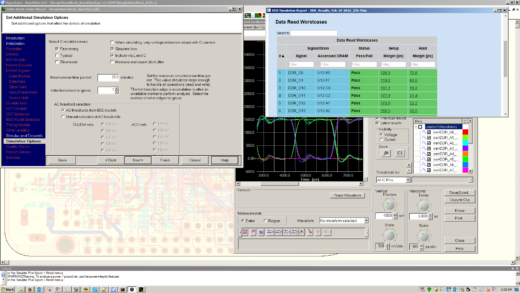

These complicated timing relationships can be difficult to analyze. To identify and resolve DDR device failures in general, or to resolve complicated timing relationships specifically, engineers need to conduct root-cause analysis which can be a tough and tedious task.

PADS HyperLynx DDR allows design engineers to simulate and analyze complex DDR circuits on their desktops to ensure an optimized product. To learn more, check out this video or request a free evaluation.

Jim

Comments

Leave a Reply

You must be logged in to post a comment.

Hello,

Does “PADS HyperLynx DDR” include portions of the interconnect that affect high-speed design DDR design, such as the FULL length of a trace which includes vias and package pin delays when these have been incorporated into the board file ?

PADS Hyperlynx just like full Hyperlynx SI/PI package can include vias. Package pin delays needs to be specified in package models (.pkg) or in RLC format under [pin] or [package] sections in the IBIS models used in the simulation. Package pin delays mentioned in constraint manager in PCB tools are not included in Hyperlynx simulations.