3D IC takes a village but must start with a netlist

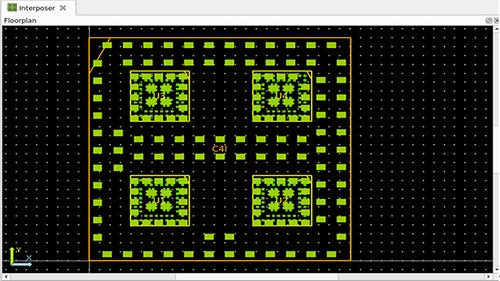

In today’s 3D IC designs, accurately capturing the complete design intent (i.e., the connectivity) of dies, silicon interposers, organic substrates and discrete components is crucial. Without a “golden” connectivity model it is very difficult to ensure a “clean” 3D IC from an assembly verification standpoint (especially LVS) before manufacturing.

Heterogeneous multi-substrate 3D ICs are especially challenging. Silicon interposers are usually owned by an IC design team with an IC design background and using IC design EDA tools and formats. Meanwhile, the organic substrate is typically owned by the package design team who have a traditional package design background and use package integration tools and formats.

In terms of design formats, the organic substrate connectivity is usually captured in a CSV file that basically includes the package bump locations, pin names and numbers, and net names. Meanwhile, silicon interposer connectivity is usually captured as a Verilog netlist. Consuming both formats require an EDA aggregation platform that allows users to modify and assign connectivity, and, eventually, combine the different netlists and generate a single system-level netlist that drives 3D IC assembly verification.

In the white paper, System-level connectivity management and verification of 3D IC heterogeneous assemblies, I discuss a workflow that lets the package architect aggregate, construct. and manage a system-level gold netlist that drives all downstream design processes. The paper will give you more insight into how Xpedition Substrate Integrator (xSI) and Calibre 3DSTACK, as part of the larger Siemens Xcelerator portfolio, will help you design tomorrow’s 3D-IC devices today.