Superior EMC Performance: Passing Class A with the Case Off

This is the final post in a three-part series discussing PCB design EMI Reduction. View the first and second.

Early in my career, I was working with a talented design group on a pretty complicated system. They did something that many other design groups did not: up-front power plane planning. They mapped out where all their signals would be routed, and made sure that the adjacent planes were either ground or the voltage that powered those nets. They also made sure that the traces did not cross any plane splits.

The resulting design was very quiet from an EMI standpoint. So quiet, in fact, that they took the case off during EMI testing to make sure the system was working! Even with the case off, the system was passing the FCC Class A limits for radiated emissions. This is a great example of how proper return path planning can result in superior EMC performance.

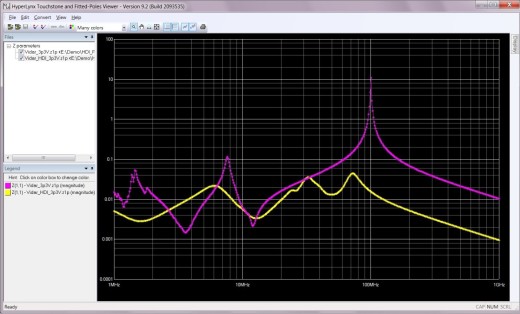

One of the optional checks in the Vertical Reference Plane Change DRC, a standard rule in HyperLynx DRC, makes sure signals reference the “correct” voltages on the PCB. This is one of the many valuable return path checks that come standard as part of HyperLynx DRC. Other return path issues, such as the “invisible” return path breaks at the ICs, can be minimized through solid PDN design with a tool like HyperLynx PI.

If you are interested in learning more, check out my recent article on Options for Reducing EMI in a PCB Design.