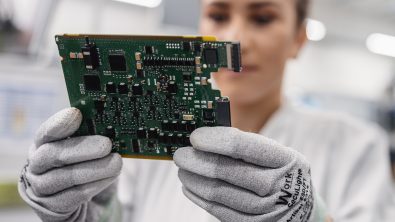

How do you manage your trace lengths?

Too often I see people just using straight length to manage their board timing. Or take it one step further and turn length into propagation delay.You know, 1 inch is about 166ps. Which is true, but nowhere near the complete picture for timing. If you think about it, the whole reason we have length constraints is to make sure data arrives at a certain time. That means that the signal switches above or below some threshold voltage at a given time. So that time also gets determined by the shape of the signal edge, which can be greatly affected by impedance and loading.

The impedance of the trace alone can have a significant effect. A 50-ohm trace versus a 25-ohm trace can impose a timing difference of around 50ps. That’s the equivalent of 300 mils of length, for a change in width of less than 30 mils. Not to mention the effects of resistors, vias, and the receivers on the chips. That is why it is so important to run even a basic signal integrity simulation to get the right timing numbers for your design. If you are just using lengths or propagation delays, you are going to be off in your calculations.

I explore this in detail in my recent article in EETimes:

Take a peek!