IoT at DAC 2017

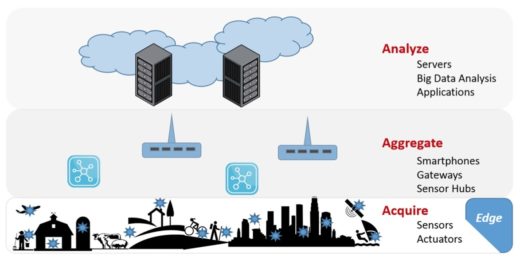

IoT has become a major topic at DAC, along with automotive. Mentor offers a unique, comprehensive solution for designing IoT edge devices that supports digital, analog, RF, and MEMS IC design, system exploration, embedded software development, PCB layout, and interactive documentation creation.

Our Tanner EDA team will be stationed in booth #1129 where they’ll have experts standing by to discuss the latest in IoT edge device design, Tanner Calibre One IC verification, the ARM DesignStart program, and more! In addition, Mentor’s booth (#947) will feature an expert panel and IoT-related technical sessions. Take a look at the lineup below and make sure to register for your favorites.

PANELS

Overcoming the Challenges of Creating Custom SoCs for IoT

The hardware industry finds itself in a new wave of innovation driven by custom SoC development for mixed-signal IoT devices. These devices span an incredibly diverse set of markets, from medical to white goods, and everything in between. With the demand for IoT connectivity and secure data management, what are the best options for today’s systems designers? This panel will explore various options and viable solutions to help designers innovate and to provide unprecedented services to the personal, industrial, and societal levels. You’ll have two chances to hear this discussion.

June 19th, 4:00pm, Mentor Booth 947

ARM, Sondrel, and Mentor

June 21st, 2:00pm, ChipEstimate Booth 347

ARM, SoC Solutions, and Mentor

TECHNICAL SESSIONS IN BOOTH #947

Mentor’s Custom/Analog Solution for IoT Edge Devices

This session will discuss the challenges of IoT edge devices, such as sensors and MEMS, then showcase several customer examples and how Mentor customers have dealt with the challenges using the Tanner platform.

How to Build a Custom SoC With Tanner AMS and ARM® Cortex®-M0

In this session, attendees will learn how they can use the Tanner AMS tools to combine their analog sensor with a Cortex(R)-M0 processor from ARM(R) to create a custom SoC. We will cover mixed-signal simulation of the analog block with a digital interface module, then connect that module to the ARM Cortex-M0 Peripheral Bus. Finally we’ll create a test program and simulate analog, digital, and software together.

What’s New in Analog/Mixed-Signal Circuit Verification at Mentor?

This session will cover the latest enhancements available from Mentor to address the significant challenges in analog/mixed-signal (AMS) circuit verification. Applications range from datacenter SoCs in the latest FinFET technology to automotive ICs implemented in BCD technology. The Analog FastSPICE Platform (BDA acquisition) provides the world’s fastest circuit verification for nanometer analog, RF, mixed-signal, memory, and custom digital circuits. For analog-centric ICs in BCD and other analog technologies, the Eldo Platform, with over 18 years of proven sign-off customer usage, offers a differentiated solution for reliability verification and comprehensive circuit analysis & diagnostics.

How to Efficiently Manage Analog Verification with Tanner Designer

In the world of analog verification, simulation results are typically managed manually, or with very expensive tools that require meticulous setup for each project and that use proprietary methods that are hard for new team members to learn and use. But, Tanner Designer is a tool that is easy to set up and that can be immediately used in your design flow to track analog simulations and to determine that each block meets specifications.

Stanford/AMD: Automated Methodology for Efficient Hardware Accelerator Design

Mobile devices today are composed of many specialized accelerators to achieve high performance and low power specifications. However, accelerator design and validation time is a limiting factor in creating these accelerator-rich SoCs. We address this problem by demonstrating the effectiveness of using new programming languages and existing hardware synthesis tools to drastically decrease the time needed to explore the design space of hardware accelerators. By pairing the image-processing language Halide with the Catapult® HLS high-level synthesis tool, different accelerator designs can be rapidly produced and evaluated for performance, area, and power.