Article Roundup: Early IC Design Verification, Semiconductor Consolidation, Emulation Platform Differences, AI in EDA & Functional Safety!

- Achieving Clean Design Early with Calibre-RTD

- The Darker Side Of Consolidation

- Not All Emulators Are Created Equal

- EDA learns to love AI

- Mentor Graphics Backs Functional Safety Bet with Austemper Design Systems

Achieving Clean Design Early with Calibre-RTD

SemiWiki

Traditional IC physical design flows require teams to complete multiple DRC runs, each taking several hours, to find and fix errors. Physical verification cycle times only stand to grow as advanced node designs increase the complexity of the task significantly. However, new technology can now left-shift physical verification into the place and route environment, enabling engineers to implement minor fixes and perform highly localized DRC runs to accelerate the design cycle.

Traditional IC physical design flows require teams to complete multiple DRC runs, each taking several hours, to find and fix errors. Physical verification cycle times only stand to grow as advanced node designs increase the complexity of the task significantly. However, new technology can now left-shift physical verification into the place and route environment, enabling engineers to implement minor fixes and perform highly localized DRC runs to accelerate the design cycle.

The Darker Side Of Consolidation

SemiEngineering

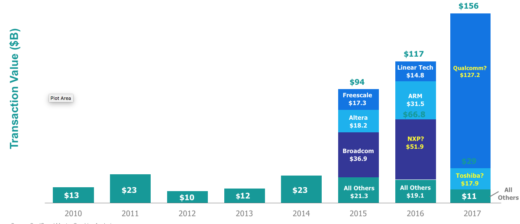

The semiconductor industry is facing a new wave of consolidation. At the same time, companies are managing increasing design complexity, greater cost and challenge of maintaining Moore’s Law, and an influx of new markets. Three major trends have emerged out of this climate: semiconductor start-up investment is increasing (particularly in AI, automotive, etc.), interest rates are rising, and large company acquisitions continue at pace with startups. This is causing chaos in the industry, making it harder for companies to provide ongoing product support, create documentation, and communicate with customers. In this article, read what industry experts have to say, including Mentor’s Wally Rhines, on this industry consolidation.

The semiconductor industry is facing a new wave of consolidation. At the same time, companies are managing increasing design complexity, greater cost and challenge of maintaining Moore’s Law, and an influx of new markets. Three major trends have emerged out of this climate: semiconductor start-up investment is increasing (particularly in AI, automotive, etc.), interest rates are rising, and large company acquisitions continue at pace with startups. This is causing chaos in the industry, making it harder for companies to provide ongoing product support, create documentation, and communicate with customers. In this article, read what industry experts have to say, including Mentor’s Wally Rhines, on this industry consolidation.

Not All Emulators Are Created Equal

Electronic Design

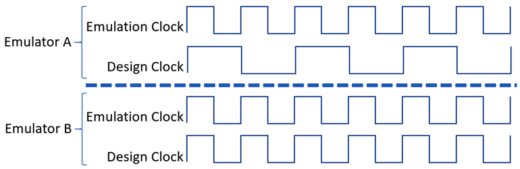

Hardware emulation has quickly become a mandatory piece of many verification toolboxes, but not all emulators are created equally. Three main parameters should be considered when evaluating the performance of an emulator: speed, throughput, and latency. This article examines each of these parameters in detail and describes how the different emulation platforms (processor-based, custom FPGA-based & commercial FPGA-based) perform in each area.

Hardware emulation has quickly become a mandatory piece of many verification toolboxes, but not all emulators are created equally. Three main parameters should be considered when evaluating the performance of an emulator: speed, throughput, and latency. This article examines each of these parameters in detail and describes how the different emulation platforms (processor-based, custom FPGA-based & commercial FPGA-based) perform in each area.

EDA learns to love AI

Tech Design Forum

Machine learning and artificial intelligence technology is slowly-but-surely penetrating electronics design methodologies. The technologies are being targeted to help accelerate and reduce the resource cost of simulation and verification tasks. However, companies implementing AI and machine learning continue to struggle with trust in the technology: how can conclusions made by machine learning and artificial intelligence programs be proven correct without duplicating their efforts?

Mentor Graphics Backs Functional Safety Bet with Austemper Design Systems

Electronic Design

The functional safety of integrated circuits has come under intense scrutiny in automotive, aerospace, and industrial applications as it can have a direct effect on the safety of humans interacting with cars, planes, and industrial equipment. Complete functional safety testing must check for systematic, malicious, and random hardware faults. As a result, Siemens has acquired Austemper Design Systems, adding robust random hardware fault safety analysis to the systematic and malicious fault tools of Mentor Graphics.