Article Roundup: Test Chips at Advanced Nodes, AI/ML Processor Design, Circuit Aging, Simulation for AVs & Konica Minolta’s HLS Success

- Test Chips Play Larger Role At Advanced Nodes

- Deliver “Smarter” Faster: Design Methodology for AI/ML Processor Design

- Circuit Aging Becoming A Critical Consideration

- Simulation in Autonomous Driving – Why Societal Change Is as Necessary as Technical Innovation

- Konica Minolta Talks About High-Level Synthesis using C++

Test Chips Play Larger Role At Advanced Nodes

Semi Engineering

Test chips are used to help design teams diagnose problems with early silicon before beginning production. The use of test chips is gaining increased popularity at 16nm, 7nm, and more advanced nodes where problems become even more costly. However, due to the cost of prototyping at these nodes, many are questioning the efficacy of this approach.

Deliver “Smarter” Faster: Design Methodology for AI/ML Processor Design

EE Times

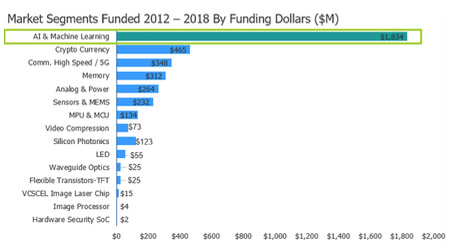

Artificial intelligence and machine learning (AI/ML) has left the confines of academia with various applications in automotive, datacenters, medical imaging analysis, and more. This is due to the availability of vast data sets, and increasingly specialized AI/ML processor IP for systems-on-chip (SoC) and standalone devices. In lockstep, the EDA industry is also embracing AI/ML to improve the accuracy and speed of design tools.

Artificial intelligence and machine learning (AI/ML) has left the confines of academia with various applications in automotive, datacenters, medical imaging analysis, and more. This is due to the availability of vast data sets, and increasingly specialized AI/ML processor IP for systems-on-chip (SoC) and standalone devices. In lockstep, the EDA industry is also embracing AI/ML to improve the accuracy and speed of design tools.

Circuit Aging Becoming A Critical Consideration

Semi Engineering

Long-term chip reliability was not a critical concern when most designs were destined for consumer electronics applications. Reliability demands are increasing as safety-conscious markets, such as medical and automotive, are becoming major semiconductor consumers. In response, EDA vendors are investing in more sophisticated chip aging capabilities to help customers achieve long-term reliability.

Simulation in Autonomous Driving – Why Societal Change Is as Necessary as Technical Innovation

Design News

Self-driving vehicle prototypes will need to be tested over hundreds of millions, or billions of miles to demonstrate their reliability and safety. This expectation creates is a substantive obstacle for the near-term viability of automated vehicles in the market. New simulation technology, however, can enable this testing to occur virtually, vastly reducing the time needed to fully test driverless vehicle systems.

Self-driving vehicle prototypes will need to be tested over hundreds of millions, or billions of miles to demonstrate their reliability and safety. This expectation creates is a substantive obstacle for the near-term viability of automated vehicles in the market. New simulation technology, however, can enable this testing to occur virtually, vastly reducing the time needed to fully test driverless vehicle systems.

Konica Minolta Talks About High-Level Synthesis using C++

SemiWiki

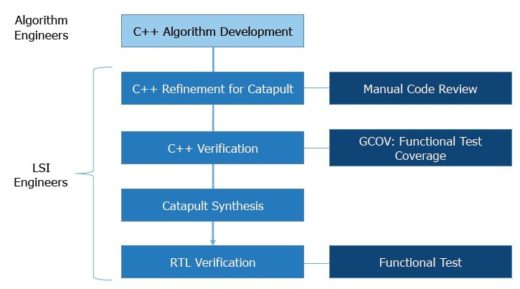

Konica Minolta has been using high-level synthesis (HLS) to increase their productivity while designing multi-functional peripherals, professional digital printers, ultra-sound equipment for healthcare and more. While adopting C++ as their design entry language has provided a number of benefits, Konica Minolta continued to struggle with manual algorithm inspection time, manual waivers to close coverage and other issues. This article describes the HLS enhancements that Konica Minolta has adopted to resolve these issues and achieve even greater design productivity.

Konica Minolta has been using high-level synthesis (HLS) to increase their productivity while designing multi-functional peripherals, professional digital printers, ultra-sound equipment for healthcare and more. While adopting C++ as their design entry language has provided a number of benefits, Konica Minolta continued to struggle with manual algorithm inspection time, manual waivers to close coverage and other issues. This article describes the HLS enhancements that Konica Minolta has adopted to resolve these issues and achieve even greater design productivity.