The Strategic Advantage in the Hardware-Assisted Verification Segment

Welcome to the Siemen hardware-assisted verification group blog. Technologies in this group include software-based tools for architectural design and verification, focus-based applications, hardware emulation, and FPGA prototyping.

We’re highlighting our differentiation in today’s post authored by Jean-Marie Brunet

Jean-Marie Brunet is Siemens EDA’s Vice President and General Manager of Hardware-Assisted Verification (HAV). He and his group recently announced the Veloce CS hardware-assisted verification and validation system including Veloce Strato CS, an emulation system; Veloce Primo CS, an enterprise-scale prototyping system, and Veloce proFPGA CS, an at-speed prototyping system.

EDA is generally a software-centric product space. So why does a hardware-oriented vendor like Siemens have a strategic advantage when it comes to chip design and verification? Because we design and verify our own chip for the Veloce Strato CS emulator.

In addition, the Veloce hardware-assisted verification portfolio is expanding rapidly and has taken a primary role in the pre-silicon verification process. It is now an integrated system of software-based tools for architectural design and verification, focus-based applications, hardware emulation, and FPGA prototyping.

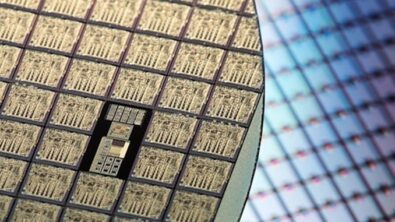

The Veloce portfolio is the perfect example of designing a chip targeted for a specific application through our hardware emulator known as Veloce. We design and verify Veloce’s Crystal chip and use the same tools we are offering customers. This makes us intimately familiar with their challenges because we are exposed to the same problems that they are, specifically how big chips get designed and verified to meet time-to-completion schedules.

Every new generation of our chip gets verified by our current hardware emulator generation, giving us insight into our customers’ challenges and credibility when we speak to them, as well as an insider’s understanding of the trends. Since we design complex devices, we know the verification trends because we’re going through them ourselves. It’s an important consideration for companies evaluating their HAV providers.

We see firsthand that verification has changed because the requirements have changed dynamically. It is no longer about making sure the chip is working. Other criteria are equally or more important now. It’s knowing what kind of verification is needed or validation may not be enough when building a chip that differentiates us. After all, our designers are no different than AI accelerator chip designers. Our designers make sure we have chips that are deliverable, whether it’s for our emulator or for a customer’s system.

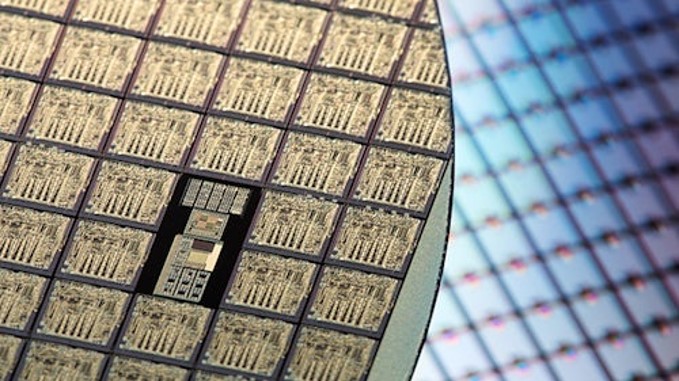

In addition to chip complexity and size, things have changed. For us, it’s the importance of yield that directly impacts margins. Our designers continually refine our processes to improve yield and consume less power. If our chip, system or emulator is going to a data center, they need to consider that the data center charges by the power plug and not by how much space is being consumed. That means power is important and the reason our system is popular with chip designers and used to verify 15-billion chip designs and larger. Speed is important and our HAV runs their workload faster.

Hardware-assisted verification is an important market segment and growing tremendously because trends are accelerating and not slowing down. Intractable chip design complexity, size and performance challenges mean this segment will continue growing for the next five years and beyond. To learn more read our latest white paper, Facing a new age of challenges in IC design.