Conversion from Vivado High-Level Synthesis (HLS) to Catapult HLS

In this blog post, we explore the key points which are required to convert an algorithm developed for Vivado HLS into Catapult HLS. Both HLS tools are very similar in their approach enabling designs to move with ease between the two tools.

High-Level Synthesis (HLS) enables us to leverage the productivity benefits of faster development and verification time associated with using a high-level language when developing algorithms and Intellectual Property (IP) blocks for implementation in Field Programmable Gate Array (FPGA) and Application Specific Integrated Circuits (ASIC). FPGA Vendors like Xilinx and Intel have their own HLS solutions for example Vivado HLS targeting vendor specific FPGA boards. Unfortunately, this also limits portability between implementation solutions.

Technology independent HLS solutions such as Siemens EDA’s Catapult provide algorithm and IP developers with the ability to create solutions for any FPGA or ASIC implementation technology.

Conversion Challenges from Vivado HLS to Catapult HLS

The typical challenges faced in this conversion can be categorized as falling within one of three classes:

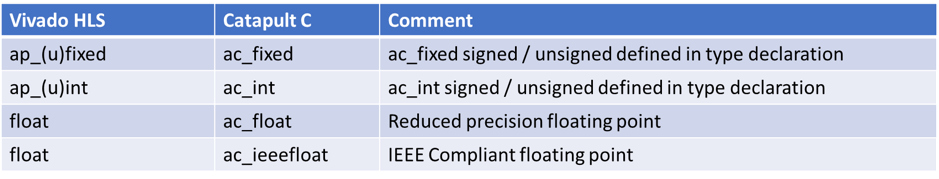

- Data Types – Support for data types varies between HLS tools, along with ambiguity between non-exact width integer types e.g. 32 or 64 bit implementations for int types depending upon operating system and processor.

- Optimization Pragmas – Pragmas used for optimization are tool specific. While they may do the same function e.g. loop unrolling or pipelining, the format and location is different.

- Libraries – Specialist HLS libraries for implementing functions such as the commonly used math library math.h may vary from vendor to vendor.

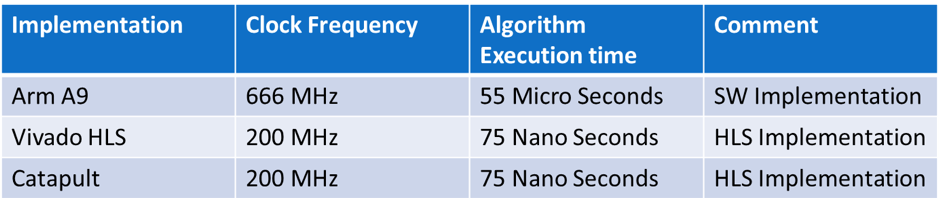

Let’s take a simple look at an AES 256 algorithm implemented in Vivado HLS and converted to Catapult. This algorithm takes 55 Microseconds to execute on the Arm A9 running at 666 MHz.

first step is to convert the data types used in Vivado HLS to their equivalent in Catapult. To aid in this conversion the table below can be used.

If the Vivado HLS design uses functions contained in the library math.h, they need to be mapped to equivalent functions the Catapult libraries ac_math.h and ac_dsp.h. These Catapult libraries can be viewed at HLSLibs.org.

To ensure optimal performance of the HLS AES implementation, the following optimizations where defined in the Vivado implementation:

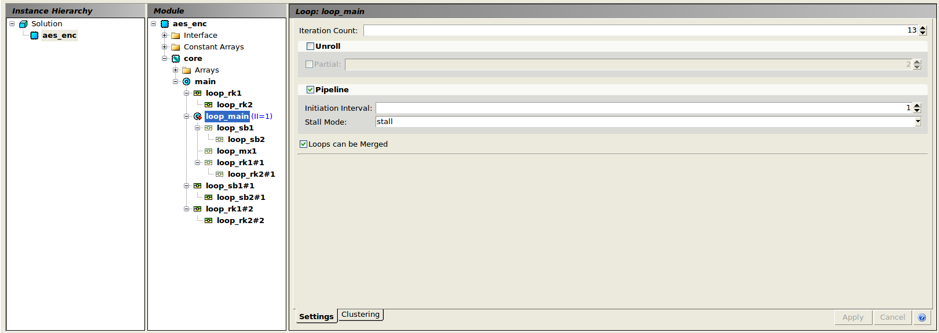

- Pipelining of Loop_Main in within the AES_ENC function.

- Unrolling of both the inner and outer loops (loop_sb1 & loop_sb2) within the SubBytes function.

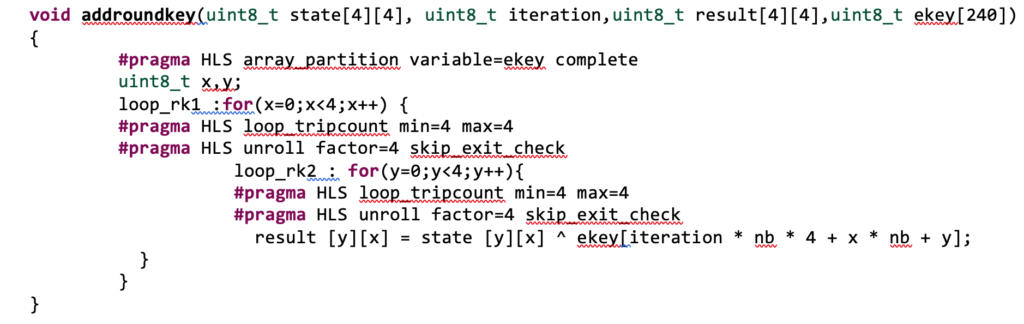

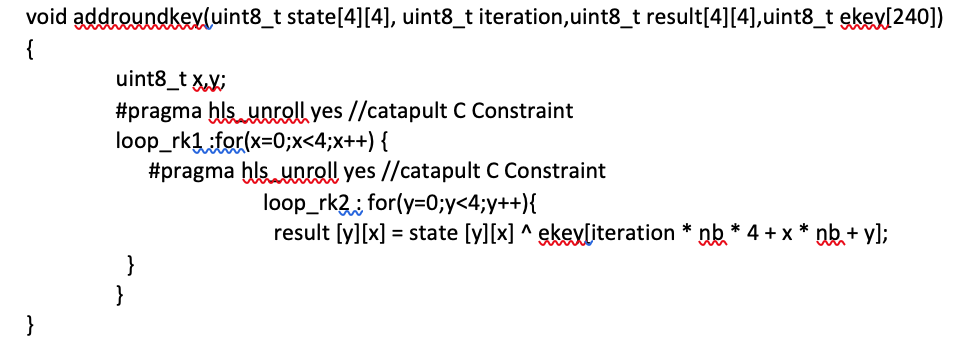

- Unrolling of both inner and outer loops (loop_rk1 & loop_rk2) in function AddRoundKey

- Complete partitioning of the EKey input in theAddRoundKey Function

- Unrolling of loop (loop_mx1) in the MixColumn function

- Inlining of the MixColumn function

- Complete partitioning of the GF2, GF3, State and Results in the MixColumn function

- Complete partitioning of the SBOX parameters within the SubBytes function

- Complete partitioning of the State and Result in the ShiftRowEnc function

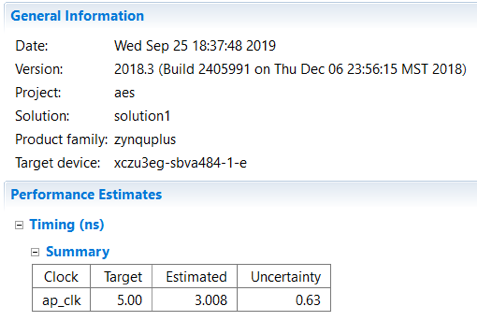

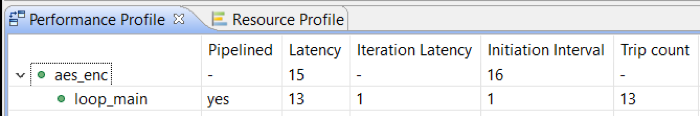

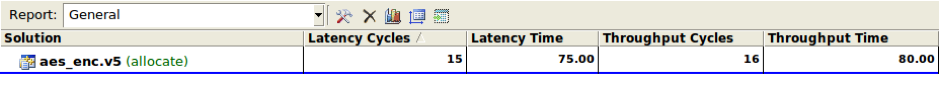

These optimizations ensure performance at 200 MHz with a 15-clock interval, when targeting a Xilinx ZCU3EG MPSoC. To achieve the same performance in Catapult we need to make some .

If a pragma is not supported by a tool it will be ignored by the compiler. Of course, we want to ensure the performance in Catapult is the same, so we need to covert the Vivado HLS pragmas to Catapult pragmas.

The key difference between Vivado HLS and Catapult optimization pragmas is the location of those pragmas. Within Vivado HLS the pragma is located inside the loop while in Catapult the pragma is located outside the loop.

Having changed the data types and pragma locations, running the source code through Catapult provides the same latency for the AES core.

Comparing the Arm A9, Vivado HLS and Catapult results, when both target a Xilinx ZCU3EG MPSoC shows Vivado and Catapult HLS implementations offer a much faster and identical implementation and iteration times.

As you can see from the conversion presented here, there is little refactoring of the code required and the main functionality of the code is left unchanged.

If you want to know more about conversion of HLS designs from Vivado HLS to Catapult HLS, you can view this white paper or view the webinar.

You can find the source code used for this blog here: https://github.com/ATaylorCEngFIET/Catapult-HLS