What’s the current state of 3D IC design?

In the first podcast about 3D IC heterogeneous integration, we talked about the disaggregation of once monolithic implementation architectures into several smaller functional chips or chiplets that are re-aggregated or integrated using a high-performance package. In the second 3D IC podcast, we discuss the current state of 3D chiplet-based designs, what’s coming next and the requirements to build a chiplet ecosystem.

Watch the 3D IC podcast episode: Current state of 3D IC design

If you prefer video to text, watch this 13-minute video on the current state of 3D IC design and developing standardized chiplet models.

We know that everyone has their own preferred learning style, and we want to make sure you can get the most out of this content in the way that works best for you. So, whether you prefer to read the copy below or watch the full episode above, we hope you find this information helpful!

Today’s typical 2.5D and 3D IC design applications

The catch-all phrase “3D IC” includes both 2.5D and 3D. Engineers use these general types of designs and technologies in packaging:

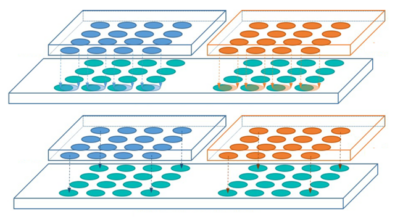

- 2.5D involves putting a chip or a chiplet on top of and interconnecting with a silicon interposer. It’s a two-dimensional integration of a chip or chiplets inside the package that form a system.

- 3D falls into two classes with the predominant type called stacked die, where you put a chip on top of another die.

The 2.5D applications currently use high bandwidth memory (HBM). These are found in high-performance computing type processes, artificial intelligence or machine learning applications where engineers want to leverage high-bandwidth memories. We use the term 2.5D because an HBM is 3D that gets integrated with other chips in a two-dimensional space.

Another type of application is taking a large design such as a complex processor and building a very large application-specific integrated circuit (ASIC). Designers break the complex processor into much smaller functional-type blocks and integrate the blocks on an interposer. This is a very specific custom design and doesn’t use general-purpose chiplets. The concept of breaking a design into smaller pieces and then connecting them on an interposer is called die disaggregation.

The 3D IC applications predominantly involve stacking either memory chips or sensors on top of another chip. Making the connection vertically stacking the die allows for a three-dimensional type implementation of the chip. Engineers can combine stacks with 2D, other 3D or single chiplets on an interposer. These are also typically very customized types of applications.

Aggregated die and 3D IC types of designs are more specialized and currently implemented by a relatively small number of companies that have very advanced IC design capabilities. It’s likely that advanced users with complex processors or sensor-based type applications will continue to dominate 3D IC applications. The predicted growth for heterogeneous integration is likely to be applications deploying general-purpose chiplet devices that integrate onto a 2.5D interposer.

General-purpose chiplets and the Chiplet Design Exchange

General-purpose chiplets can leverage this specific technology and optimize it for a particular application. The chiplet marketplace can follow the same model as the established HBMs but will need a chiplet ecosystem. The chiplet ecosystem requires each chiplet IP device to include a standard set of models and vendors to adopt amended workflows and new business models.

The Chiplet Design Exchange (CDX) is a working group formed under the ODSA with a charter to standardize chiplet models and deliverables as well as system and package workflows to facilitate chiplet ecosystems. Siemens’ Advanced Packaging Solutions Director and voice of the 3D IC design podcast, Tony Mastroianni is part of the CDX group.

The group recently delivered a white paper that proposes a set of standardized chiplet models at the IEEE 3D IC conference late last year. This diverse set of contributors came up with a comprehensive list of about ten different categories in over 30 different models for general-purpose templates.

With the introduction of the models, the next step is the general adoption or refinement by prospective chiplet vendors. Once there’s commitment, teams need updated EDA workflows to support designing and consuming the models proposed. And then eventually, the general design user base to adopt the tools and the methodologies to build these types of systems.

Standardizing on a common set of chiplets deliverables seems like a good start towards establishing an ecosystem.

Want to learn more about 3D IC? Listen to the podcast now, available on your favorite podcast platform.

View the episode transcript

[00:10] John McMillian: Welcome to the Siemens EDA podcast series on 3D IC Chiplet Ecosystems, brought to you by the Siemens Thought Leadership team. I’m your host, John McMillian. In our first podcast on 3D IC Heterogeneous Integration, we talked about the disaggregation of once monolithic implementation architectures into several smaller functional chips or chiplets, which are then re-aggregated or integrated using a high-performance package. If you missed that episode, we encourage you to check it out in the Siemens podcast community blogs. Today, in our second podcast of the 3D IC series, we will discuss the current state of chiplet-based designs, the future direction, and what is required to facilitate a chiplet ecosystem. I’m pleased to be joined again by my special guest, Tony Mastroianni, who is the Director of Advanced Packaging Solutions at Siemens Digital EDA. Welcome, Tony. And thank you for taking the time to talk with me again today about chiplet ecosystems. And before we dive into the discussion, would you mind giving our listeners just a brief recap of your current role and background?

[01:13] Tony Mastroianni: Sure, John. Currently, I’m responsible for driving the advanced packaging design flows and methodologies at Siemens EDA. My background, historically, has been in IC design and project management. More recently, prior to Siemens, I was involved in actually developing advanced package design flows for a fabless semiconductor company.

[01:38] John McMillian: Thanks, Tony. Before we look ahead, let’s take a look back and discuss the current state of heterogeneous integration. Can you please tell us what types of applications and packaging technologies are currently deploying 3D IC methodologies?

[01:51] Tony Mastroianni: Really, when we talk about 3D IC, it’s kind of a catch-all phrase, but it really includes two-and-a-half D and 3D. So, two-and-a-half D applications involve putting a chip or a chiplet on top of a silicon interposer, and those devices are interconnected on that interposer. So it’s really a two-dimensional integration of chip or chiplets inside the package, forming a system. 3D falls into two different classes. And today, the predominant type of 3D is what we call stacked die, that’s where you put one chip on top of another die. So, those are the general types of designs and technologies that are used in packaging. The two-and-a-half D applications currently use HBM memories. And these are used in high-performance-compute type processors, and artificial intelligence or machine learning applications where they want to leverage these high-bandwidth memories or HBMs. Another type of application that deploys 2D type of heterogeneous integration. And we use the term two-and-a-half D because an HBM memory is 3D, and that it gets integrated with other chips in a two-dimensional space. So, it’s really a two-dimensional integration, but you can have either 3D chips or chiplets, or 2D. So, that’s where the “two-and-a-half D” term came from. So, the other type of application would be, actually, taking a large design such as a complex processor – AMD and Intel are deploying these techniques – and essentially, rather than building a very large ASIC and having a complex processor in a single chip, they actually break that processor up into much smaller blocks – functional type blocks – and essentially, those get integrated on an interposer. It’s really very specific to a very custom design; it’s not really using general-purpose chiplets, which we’ll talk about later, but it’s actually breaking a design into smaller pieces and then connecting those in an interposer. So, this is what we call die disaggregation. Now, currently, 3D applications are predominantly stacking either memory chips or sensors on top of another chip. So, again, these are typically very customized type of applications as opposed to general-purpose chiplets. Just making the connection vertically by stacking the die allows three-dimensional type implementation of the chip, and that can be combined with 2D; so you can actually stack die on top of each other and also combine them with other either 3D or single chiplets on an interposer. So, this aggregated die and 3D type of designs, they’re more specialized and they’re currently being implemented by a relatively small number of companies that have very advanced IC design capabilities.

[05:14] John McMillian: It’s interesting. So, today, since only a small number of sophisticated users are doing these types of designs, where do you see the industry heading to expand the adoption of 3D IC into a broader set of applications and user base?

[05:29] Tony Mastroianni: For the foreseeable future, I think 3D applications will continue to be dominated by these advanced users doing complex processors or sensor-based type applications. The explosive growth that we’re predicting with heterogeneous integration is really likely to be dominated by applications deploying general-purpose chiplet devices that are integrated onto a two-and-a-half D interposer.

[05:57] John McMillian: So, Tony, what types of chiplets are available today? And what type of new chiplets do you anticipate coming to market?

[06:05] Tony Mastroianni: So today, I would say, arguably, HBM memories really are the only general-purpose chiplets that are on the market today. And they’re used in the applications such as – I talked about earlier – the high-performance compute and AI-type of applications. Now, I did talk about die disaggregation of these complex processor type of applications, and that’s basically splitting a very customized chip into many pieces. IP disaggregation would actually be a similar approach but rather than breaking a custom chip into separate pieces, you would actually replace special purpose IP that would normally be implemented inside the chip or a System On Chip – as it’s referred to SOC – and you would actually replace that with a special purpose IP chiplet. And rather than integrating that IP inside the ASIC, you would integrate that IP in your system in the package on an interposer. So this is what, again, what we would call IP disaggregation. And these IP chiplets can include functions such as high speed, long-reach SerDes, high-performance analog, RF, or specialized processors – really, it’s a broad set of general-purpose, reusable chiplets that would be sold out in the marketplace. And they can be used as building blocks in a system and package as opposed to IP that is sold as general-purpose IP building blocks to be integrated into a chip.

[07:43] John McMillian: So I suspect these general-purpose chiplets will be offered by a host of vendors implemented in an ASIC process best suited for their IP. But what is required to drive the adoption of this broader set of general-purpose chiplet devices?

v[07:58] Tony Mastroianni: That’s a good point. These chiplets can leverage this specific technology and process to optimize it for that particular application. What I believe is going to drive this market are the large marketing projections that should hopefully motivate the vendors to consider this new chiplet market. So, HBMs have been around for several years and that’s a huge market. This chiplet marketplace, we think, can follow the same model. In order to support this, though, it is going to require a chiplet ecosystem. And that will require each of the chiplet IP devices to include a standard set of models, as well as workflows, as well as new business models. So, there are, certainly, benefits of the chiplet-based approach, but it is going to require a different set of deliverables from the chiplet vendors, different workflows, and different business models. So, the Chiplet Design Exchange is a working group that I’m actually a member in, and the charter is to standardize chiplet models and deliverables as well as system and package workflows to facilitate chiplet ecosystems. So, this group was formed under the ODSA, a working group. We’ve been around for about two or three years. We’ve had just recently written a white paper and delivered that at an IEEE conference, proposing a set of standardized chiplet models. And this was presented at the IEEE 3D IC conference last November at NC State. So, the first step will be for the general adoption or refinement of these models by prospective chiplet vendors. So, following that, we’ll need the EDA workflows that can support designing these type of templates, as well as being able to consume the models that we’re proposing to support these chiplet models. And then eventually, we’ll need the general design user base to adopt the tools and the methodologies to build these types of systems.[10:18] John McMillian: So, standardizing on a common set of chiplets deliverables seems like a good start towards establishing an ecosystem. What kind of models is the CDM group recommending? And where can someone learn more about the models?

[10:31] Tony Mastroianni: John, we put a lot of thought into this, and we did have a diverse set of contributors as part of the working group, and we came up with a comprehensive list of about 10 different categories in over 30 different models that we’re recommending to be provided with these general-purpose templates. So, these categories include functional models, physical models, power, timing, models required to support signal and power integrity analysis, electrical analysis as test, and security is also going to be an important issue. So, these are all the different classes of models that are going to be required to support these SiP flows from the chiplet vendors. So, we’ve made strong recommendations that these models be machine-readable, but there will still be some level of documentation also required. So, with regards to your question for getting more information, probably the best place to start would be in reading the white paper. And we also invite anyone to join the CDX working group and participate.

[11:44] John McMillian: Thanks again, Tony, for this highly informative discussion on chiplet ecosystems in the second episode of our 3D IC series. We’re at the time for now but we’re looking forward to a future podcast with you on the evolution of the 3D IC workflows coming soon. Thanks again, and thank you all for listening and joining us today.

[12:01] Tony Mastroianni: Thank you, John, as well.

About the Siemens 3D IC Design flow

The Siemens 3D IC Design Flow is a comprehensive set of tools and workflows targeted to develop advanced 2.5 and 3D IC heterogeneous system-in-package (SiP) designs. This proven, complete 3D IC design flow includes 3D architecture partitioning to planning, layout, design-for-test, thermal management, multi-die verification, interconnect IP, manufacturing signoff, and post-silicon lifecycle monitoring. Transform existing design and IP architectures into chiplets or build scalable 3D IC technology for faster time to market.

Learn more about Siemens EDA’s marketing-leading 3D IC technology solution: https://www.siemens.com/3dic