The Five Keys to Next-Generation IC Packaging Design: Part 1

Part 1: An advanced IC packaging design and verification solution

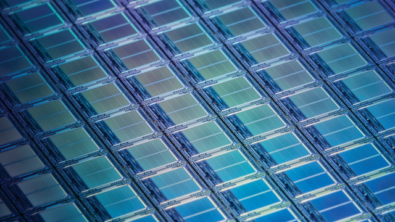

For many applications, next generation IC packaging is the best path to achieve silicon scaling, functional density, reduced overall package size, and heterogeneous integration. Heterogeneous and homogeneous integration offers a path to enhanced device functionality, faster time-to-market, and silicon yield resiliency. Multiple integration technology platforms have emerged that allow for cost, size, performance, and power optimizations that satisfy the need of multiple markets, such as mobile computing, automotive, HPC, AR/VR, AI, IoT, medical, aerospace, and 5G.

Problems with next generation IC packaging

However, these packages present unique challenges for traditional package design tools and methodologies. Design teams must work together to verify and optimize the entire system, not just the individual elements. Traditional IC packaging substrate design is typically very similar to a small-scale laminate and/or build-up-based PCB. It is often manufactured by traditional PCB fabricators and usually designed with modified PCB tools.

In contrast, today’s advanced packages use manufacturing techniques, materials, and processes that have increasingly more in common with silicon foundry processes and require a new approach for design and verification at all levels.

One of the first challenges a design team must overcome is the accurate aggregation of substrates —which can be both active and passive — and discrete devices. These substrates and devices come from multiple sources and suppliers and, most likely, are available in multiple and often different formats.

A comprehensive design and verification solution

Given the multiple data sources and formats, a comprehensive verification flow is required — one that accounts for assembly-level physical verification, as well as more in-depth, system-level electrical, stress, and testability verification. Also needed are design tools that deliver fast, accurate, and automated flows to ensure that market schedules and performance expectations can be met. Ideally these flows provide a single integrated process built around a 3D digital model, or digital twin, of the entire heterogeneous package assembly.

These next-generation IC packages need a next-generation design and verification solution that incorporates and supports digital prototyping, multi-domain integration, scalability and range, precision manufacturing handoff and finally golden signoff. The foundation or bedrock of such a solution is a true digital twin or virtual model of the entire design assembly. This provides a comprehensive representation of the full system comprising multiple devices and substrates. The digital twin enables automated verification of heterogeneous assemblies beginning with substrate-level DRCs and expanding into layout versus schematic (LVS), layout-versus-layout (LVL), parasitic extraction, stress and thermal analysis, and, finally, test.

Interested? Then download and read this white paper to learn more!