Shifting left for earlier testing in 2.5D and3D IC design

In our last 3D IC blog, we talked about the impact of 3D IC on device reliability. In today’s blog, we discuss the importance of adopting a shift-left strategy for complex designs that integrate multiple dies into a package. We’ll examine the challenges and opportunities for performing comprehensive tests on 2.5D and 3D IC designs. Learn about the factors teams need to consider when planning for 3D design-for-test (DFT) and IP tests and complete multi-die packaged product testing.

Watch the 3D IC Podcast Episode about Uncovering 2.5D and 3D IC Tests

If you prefer video to text, watch this 21-minute video about shifting left and the factors teams need to consider for 2.5D and 3D IC tests.

We know that everyone has their own preferred learning style, and we want to make sure you can get the most out of this content in the way that works best for you. So, whether you prefer to read the copy below or watch the full episode above, we hope you find this information helpful!

Fitting DFT and IP tests into 3D IC design and manufacturing phases

Design-for-test (DFT) is structured logic designers insert into the chip during the chip design phase. DFT logic makes the chip easier to test while forcing the chip into all possible defect states. Teams may also insert hardened intellectual property (IP) cores during the design phase. They must integrate DFT and IP core-specific features into the overall DFT and test access scheme.

For 2.5 D and 3D IC designs, there are extra steps to insert logic that provides test access to each die, including new capabilities for die-to-die interconnect testing. The verification phase is a big step with logic insertion and thoroughly verifying the DFT and test logic before creating chip masks and sending parts to manufacturing.

Teams must also generate the DFT and IP test vectors applied to the chip during manufacturing testing. There are two major activities on the manufacturing side:

- Wafer or Known Good Die (KGD) test: includes the die-level tests created in the design phase

- Package test: includes die-level tests completed during KGD, and specific tests for 3D test access in die-to-die interconnect testing

The primary difference between 2D regular chip testing and 2.5D/3D chip testing is adding a die-to-die interconnect test.

3D IC design DFT and product test challenges

System-in-Package (SiP) architecture bundles multiple dies inside the same package. For example, putting a system in the package that includes 2.5D and a 3D stacked die. From a testing perspective, the 2.5D and 3D require a die-to-die (D2D) interconnect test as well as an individual die test—repeated from the wafer test to the package level.

The key to accomplishing 3D tests is test access.

But how do teams initialize and test that middle die in the 3D stack and how do they initialize and test just the IO buffers and die-to-die interconnects within the SiP? For common interfaces, how do we apply scanned pattern data to just that middle die in the stack and test the chip digital logic?

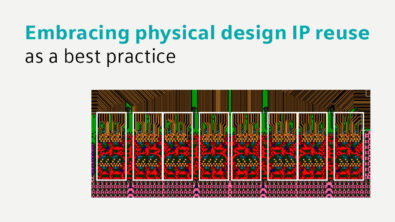

The first step is ensuring we have common interfaces between each die to enable clean communication between the dies. Teams also need to expand DFT planning and collaboration to include physical design and package engineering—for example, SiP test IO spec needs to be defined at the interposer for 2.5D or through-silicon via level for 3D.

Testing teams must also be aware of compatible die selection criteria and binning for dies from different processes. There could be a mix of parts from 7 nm, 3 nm, 5 nm, and 14 nm on the same package. Teams must build a strategy to ensure these parts are compatible from a timing perspective. We need die-level test access to the package IOs to run the full suite of the SiP-level package test, burn-in reliability screening and split corner characterization to see at what extremes of process temperature and voltage we can run the test. Teams must also be aware of any possible thermal and power issues during the test. Test activity factors can often exceed functional ones, so we need to be mindful of that.

Teams must be aware of enhanced DFT planning for the IO spec and interface, multi-die, and chiplet packages. We must also be mindful of comprehensive KGD testing at the wafer chiplet level to provide thoroughly tested bare dies for assembly into the SiP.

Comprehensively tested bare dies are a real challenge because the wafer probe level can be very noisy, and power limited. But we must run the entire test program at the die level to ensure those bare dies perform properly before assembling them into an expensive package.

We need close collaboration on system-level testing as we move systems into the package. For example, for 2.5D, we need to run board-level die-to-die interconnect testing inside the package using the IEEE-1149.1 boundary scan. This scan was typically only run at the system or board level in the past, but now we’re doing it inside the package.

Implementing DFT and IP test methods for 2.5D and 3D IC designs

There are some DFT and IP test methods that 2.5D and 3D IC design teams should implement to ensure high defect coverage and reliability.

Early in the ASIC or chiplet IO development phase, teams need to generate and insert primary TAP (PTAP), secondary TAP (STAP), as well as Flexible Parallel Ports (FPP) following the IEEE 1838 standard for 3D IC test. We also need to generate and insert 1149.1 compliant TAP for the entire package assembly to test this part at the whole board level, and it’ll look like a regular chip. We want to shift left to the RTL phase as much as possible to implement DFT and IP tests, and that gives us an early view of DFT for the physical design teams.

Teams also need to be in tune during every phase with the multi-die and package-level engineering teams to include the test bus planning and routing, the test timing between dies, functional and timing simulation reports, and wafer-level die test and planning and validation. We’ll also generate die-to-die boundary-scan-based interconnect patterns and extract package level boundary scan or a BSDL file that goes on to board test for board-level testing. Then we’ll create and insert in IEEE 1687 IJTAG network that will use to initialize the tests inside the part and run some of the tests inside the part as well. So, IEEE 1687 is used for both DFT and IP testing.

Die and package level planning interactions for 3D IC DFT and IP tests

DFT and IP tests are critical for multi-die integrated designs and cannot be ignored or left as an afterthought. Accommodating 3D DFT and IP tests means thinking about what die and package level planning interactions we need for physical design, power analysis, packaging, and test hardware.

DFT and IP tests are critical for multi-die integrated designs and cannot be ignored or left as an afterthought. Accommodating 3D DFT and IP tests means thinking about what die and package level planning interactions we need for physical design, power analysis, packaging, and test hardware.

Today, we don’t have the technology to build probe cards that have the fine pitch and reliability of the standard probe card for KGD testing. The probe has very tight spacing for micro bumps that both 2.5D and 3D chips use and is a much finer pitch than standard bumps. To get around this, we put in sacrificial pads at standard bump spacing and build a probe card that can probe those, provide all the tests required signals, and provide a sampling of power and ground.

If not done right, we can end up burning probe tips and end up with excessive IR drop and noise. Being aware of the power analysis, thermal analysis and reliability is critical. Reduced power and ground can cause false failures due to IR drop, and we throw away good parts, impacting yield. Since the test patterns can have very high activity factors, we need to run both power and thermal analysis in all the test modes at the individual die and SiP levels.

Power control capabilities of the DFT tool should also be used, the packet-based scan, and then chiplet placement and alignment of the die-to-die test interfaces are important because the package team will provide that to us for use during SiP-level physical planning process.

DFT designers need to be interactively driving forward the test interface requirements and working with both the packaging and physical design teams. DFT designers need support from the package team to generate the SiP-level die wrapper netlist and parasitic extractions that are necessary to do die-to-die STA and timing simulation of the test interfaces. Those high-speed test interfaces may also require a high-speed signal integrity analysis from the package design team as well.

Developing a fully testable 3D IC design

Designing a fully testable 3D IC design or multi-die architecture requires the design and test teams to collaborate as early as possible. Design teams must incorporate several DFT standards that can be effectively integrated and packaged into the SiP:

- IEEE 1838: 3D IC test

- IEEE 1687: IJTAG used for die-to-die (D2D) testing initialization and getting results from DFT and IP core testing

- IEEE 1149.1 and 1149.6: D2D interconnect testing for both 2.5D and TAP for IO-level boundary scan and IJTAG.

Specific IP test modes for those standards mentioned, like UCIe, HBM3, OpenHBI, BoW, or others, need to be implemented into the functional SiP design. And then the die-and-test method compatibility is also essential for SiP dies and chiplets from different process nodes that may require special binning and storing of signatures inside OTP or e-fuses. Teams must conduct full testing at the die-level, common, functional, and interface between the die.

2.5D or 3D IP core testing

IP cores come from third-party providers; similarly, chiplets may also come from third-party providers. With these chiplets, there’s a possibility of things like SerDes, DDR, HBM Phy’s, PLLs and DLLs that need testing. We can’t leave tests as an afterthought.

In the past, IP vendors often shipped their IP cores with just a Verilog test bench at the IP level and then left it as a user exercise to map and cycle those patterns up to the top level. If we have that challenge, 2.5D and 3D bring additional complexity.

We add a new level of hierarchy for 2.5D and 3D above the top level of the chip that incorporates all chips; this is where a wrapper netlist comes in. IP vendors increasingly ship their IP cores with internal JTAG (IJTAG) with a couple of files:

- ICL: a hardware description of the test interface

- PDL: a pattern description

With these two files and commercial IJTAG tools, you can generate up to the top level of the SiP, the test benches and production test vectors.

3D IC testing and reliability: burn-in testing and voltage stress

In the 3D IC reliability blog, we talked about testing for thermal and power reliability issues as well as burn-in testing and voltage stress.

Burn-in is where we put a sample of parts into the burn-in oven where we raise the voltage and temperature to emulate many years of operation. For example, we can keep the parts inside for 2000 hours and emulate approximately ten years of life, depending on the temperature. We continually run all our package-level SiP tests and take the parts out regularly to test them on a production tester or automatic test equipment (ATE) to see if any parts fail. If there’s a failure, we complete a failure analysis (FA). In the FA lab, we repair the parts, find out what happened and correct it.

Conducting voltage stress with the right voltage level for the right duration and the right ramp time can closely emulate burn-in but in just 100 ms or so of production testing. This test provides an opportunity to degrade or destroy marginal parts that might fail later.

Want to learn more about the impact of 3D IC the front-end of design? Listen to the podcast now, available on your favorite podcast platform.

Expand to see the Transcript

[00:10] David Lyell: Welcome to Siemens EDA podcast series on 3D IC design brought to you by the Siemens Thought Leadership Team. In our seventh podcast on 3D IC Reliability, we discussed the impact 3D IC design has on device reliability, ranging from understanding thermal interactions between devices to the related thermomechanical stress that can lead to warpage and design failure. Today, we will discuss the impact that 3D IC design has on test, ranging from design for test or DFT and IP testing, through to complete multi-die packaged product test. I am pleased to introduce my special guest, Joe Reynick, who is the Tessent Product Engineering Manager for Siemens EDA. Welcome, Joe. Thank you for taking the time to talk with me today about the 2.5D and 3D IC Tests. Before we dive into the discussion, would you mind giving our listeners a brief description of your current role and background?

[00:01:01.07] Joe Reynick: Sure thing. Thanks for the introduction, David. Thanks, everybody, for inviting me here today to talk to you about multi-die, 2.5D, and 3D IC Test. Just as a background, my current responsibilities include Product Engineering Manager for the Tessent suite of tools from Siemens EDA, and that’s a division of Siemens Digital Industries. As background, I have 37 years of direct experience in ASIC design, optoelectronics, design for test, IP test and silicon bring up, and EDA. My prior experience was at eSilicon, which is now a part of Marvell and Bell Labs. Currently, I’m responsible, as I mentioned, for product engineering of the Tessent DFT tool suite.

[00:01:44.25] David Lyell: Very good. Joe, can you give us a brief overview of how DFT and IP tests fit into the design and manufacturing phases for 3D chips?

[00:01:53.28] Joe Reynick: So, first of all, DFT means Design For Test, which is structured logic that we insert into the chip during the chip design phase. That DFT logic just makes the chip easier to test while forcing the chip into all possible defect states. So, hardened IP cores may also be inserted during the design phase. And these cores may also have DFT and IP core-specific features that need to be integrated into the overall DFT and test access scheme. So, for 2.5 D and 3D, we have extra design steps to insert logic that provides test access to each of the dies, including new capabilities for die-to-die interconnect testing. Besides logic insertion, we also need to thoroughly verify the DFT and test logic before creating the chip masks and sending the part to manufacturing — so, that whole verification phase is a big step. We also need to generate the DFT and IP test vectors that will be applied to the chip during manufacturing test. So, on the manufacturing side, we have two major activities: wafer test, which we also call KGD or Known Good Die test, which includes the die-level tests that we created in the design phase; and package test that includes those die-level tests that we did during KGD, and the specific test for 3D test access in die-to-die interconnect testing. So, that’s the main difference between standard, just fixed 2D regular chip test; with 2.5D and 3D, we add the feature of die-to-die interconnect test.

[00:03:35.00] David Lyell: Fascinating. Joe, there’s been a great deal of growth and development around advanced multi-die heterogeneous packaging over the past several years. Aside from design and analysis, what challenges do heterogeneous assemblies need to overcome for DFT and production test?

[00:03:51.20] Joe Reynick: First of all, a little bit of a definition. In previous installments of our podcast series, we covered SiP or System-in-Package architecture. So, when you hear us say SiP, it’s talking about having multiple dies inside the same package — basically, we’re putting a system in the package that’s comprised of 2.5D, which is like MCM on steroids, and then 3D which is stacked die. So, both 2.5D and 3D require die-to-die interconnect test and the individual die test that we talked about to be repeated from the wafer test to the package level, and they’re typically run at different temperatures. So, the keys to accomplishing 3D tests are, as mentioned, test access. So, how do I initialize and test just that middle die in the 3D stack? Or how do we initialize and test just the IO buffers and die-to-die interconnects within the SiP? And then on common interfaces, how do we apply scanned pattern data to just that middle die in the stack and test all of the chip digital logic? So, we need to make sure that we have common interfaces between each of our dies, so that we can communicate cleanly between the dies. We also want to expand the DFT planning and collaboration to include physical design and package engineering — for example, SiP test IO spec needs to be defined at the interposer for 2.5D or through-silicon via level for 3D. We may also add sacrificial pads for Known Good Die or KGD wafer probe—we’ll talk a little bit more about that later—and common die-to-die test interfaces are required for all chiplets. So, compatible die selection criteria and binning for dies from different processes we need to be aware of as well. We may be mixing matching parts from 7 nanometers, 3 nanometers, 5 nanometers, and 14 nanometers on the same package. So, we need to make sure from a timing perspective, for example, that these parts are compatible, so we have to come up with strategies for doing that. And then die-level test access to the package IOs is needed for running the full suite of the SiP-level package test, burn-in reliability screening, and split corner characterization to see at what extremes of process temperature and voltage can we run the test.

[00:06:16.20] Joe Reynick: We also need to be aware of thermal and power issues that we talked about in our seventh podcast — for example, IR drop inside the package, any thermal excursions that could be going on during test. And test activity factors can often exceed functional activity factors, we need to be aware of that. So, packet-based scan from nonoverlapping scan clocks is also a useful technique for keeping IR drop under control. And a little shameless plug: If you look at poster 18 at the 2022 International Test Conference—it’s in the proceedings there or online—you can see a good paper on IR drop and control using packet base scan. So, then the use of hierarchical DFT for 2.5D and 3D package assemblies or a mixture of both in the same SiP can exist. We call that 5.5D, actually. A good example of that is HBM, where we have 3D stack and 2.5D host die on the interposer — so, 2.5 plus 3 is 5.5, so we get that from the IEEE 1838 3D test standard. Adherence in support of interface standards is really important, especially for 2.5D SIPs, and that includes emerging and established standards like HBM3, UCIE, Bunch of Wires (sometimes called BoW), and OpenHBI. These usually include special die-to-die phy tests that need to fully test these interfaces — so, often included with the IP core itself. And these phy’s often incorporate new tests and reliability methods like IO BIST with Lane Redundancy to repair defective connections between the dies. And these methods can be also independently implemented at the chip level. We have to be aware of enhanced DFT planning for the IO spec and interface, multi-die, and chiplet packages. We have to also be cognizant of comprehensive Known Good Die testing at the wafer chiplet level to provide fully tested bare dies for assembly into this System in Package. So, these fully tested bare dies are a real challenge because the wafer probe level can be very noisy and power limited. But we have to run the full test program at the die level, and make sure those bare dies are fully good before we’re trying to assemble them into a multi $1,000 package — we don’t want to be throwing away those expensive parts. And then we need closer collaboration with system-level testing, so we truly are moving systems into the package — for example, for 2.5D, we need to run board-level die-to-die interconnect testing inside the package using IEEE-1149.1 boundary scan, which was typically only run at the system or board level in the past but now we’re doing it inside the package. We also need to do die-to-die at-speed interconnect testing — so, in addition to things like IO BIST and Lane Repair, we may have USR and XSR SerDes, we may have things like at-speed scan as well. So, that’s pretty much the things that we need to be aware of for 2.5D and 3D Test.

[00:09:36.29] David Lyell: Interesting. Given the comprehensive nature of ensuring high defect coverage and reliability, what DFT and IP test methods should the DFT and IP test team implement?

[00:09:48.26] Joe Reynick: First of all, early in the ASIC or chiplet IO development phase, we need to be able to generate and insert primary TAP, secondary TAP, as well as what they call FPP or Flexible Parallel Ports, following the IEEE 1838 standard for 3D IC test. It’s also important to generate and insert 1149.1 compliant TAP for the entire package assembly so that we can actually test this part at the true full board level, and it’ll look like a regular chip. We want to shift left to the RTL phase as much as possible to implement DFT and IP test, and that gives us an early view of DFT for the physical design teams. And then we need to be very in phase with the multi-die and package-level engineering teams to include the test bus planning and routing, the test timing between dies, functional and timing simulation reports, and wafer-level die test and planning and validation. And then we’ll generate die-to-die boundary-scan-based interconnect patterns. We’ll extract package level boundary scan or BSDL file that goes on to board test for board-level testing. Then we’ll create and insert in IEEE 1687 IJTAG network that will use to initialize the tests inside the part and actually run some of the tests inside the part as well. So, this IEEE 1687 is used for both DFT and IP testing.

[00:11:23.03] David Lyell: So, it’s obvious that DFT and tests are critical for multi-die integrated designs and cannot be ignored or left as an afterthought. So, what die and package level planning interactions do we need for physical design, power analysis, packaging, and test hardware to accommodate 3D DFT and IP test?

[00:11:44.21] Joe Reynick: One that jumps out right away is at KGD wafer probe, we don’t have the technology there today to build probe cards that have the fine pitch and reliability of a standard probe card for Known Good Die testing. And the reason for that is that the probe card has very tight spacing for micro bumps, which both 2.5D and 3D chips are using. It’s a much finer pitch than standard bumps. So, what we do to get around this is we put in something called sacrificial pads that are at standard bump spacing and we can build a probe card that can probe those, provide all of the tests required signals, and then be able to provide a sampling of power and ground. And we have to be very careful with that because if we don’t get it right, we can end up burning probe tips, we can end up with excessive IR drop and noise. So we definitely need to be in touch with the power analysis and the thermal analysis and reliability. So, reduced power and ground can actually cause false failures due to IR drop, so you end up throwing away good parts which affect your yield. We talked about the test hardware reliability due to the high current density at the probe pins since we don’t have all of the power and grounds available to us. And then we need to make sure that since the test patterns can have very high activity factors, we need to run both power and thermal analysis in all the test modes, both at the individual die and SiP level. Power control capabilities of the DFT tool should also be used, and as the aforementioned packet-based scan, if you have that capability, and then chiplet placement and alignment of the die-to-die test interfaces are important because the package team will provide that to us for use during SiP-level physical planning process. So the DFT designers need to be interactively driving forward the test interface requirements and working with both the packaging and physical design teams. And then finally, support from the package team is also needed to generate the SiP-level die wrapper netlist and parasitic extractions that are necessary to do die-to-die STA and timing simulation of the test interfaces. Those high-speed test interfaces may also require a high-speed signal integrity analysis from the package design team as well.

[00:14:20.13] David Lyell: So, designing a fully testable SiP requires the design and test teams to collaborate as early as possible. What other factors do we need to consider for a 3D test?

[00:14:30.18] Joe Reynick: So, designing dies for a System-in-Package or multi-die architecture has to incorporate several DFT standards that can be effectively integrated and packaged into the SiP. And these standards include IEEE 1838, we talked about earlier, which is for 3D IC test; IEEE 1687, which is IJTAG we use for die-to-die testing initialization and getting results from DFT and IP core test. We also use 1149.1 and 1149.6 for die-to-die interconnect testing for both 2.5D and TAP for IO-level boundary scan and IJTAG. For 2.5D, we’re actually doing a board-level boundary scan inside the package again, so that’s a sort of a new capability. Specific IP test modes for those specific standards that we talked about like UCIe, HBM3, OpenHBI, BoW, or others need to be implemented into the functional SiP design. And then the die-and-test method compatibility is also important for SiP dies and chiplets from different process nodes that we talked about may require special binning and storing of signatures inside OTP or e-fuses. And also running full die-level, common, functional, and test interfaces are needed to be between the die. So, we have to make sure that we have the same interfaces between dies, or the two dies just won’t talk to each other.

[00:16:00.22] David Lyell: Now, we didn’t talk much about the 2.5D or 3D IP test. Can you say a few words about IP core testing?

[00:16:09.07] Joe Reynick: So, what are IP cores? First of all, these are cores that you get from third party providers. Now, we have a new market for chiplets as well, which also might come from third party providers. And in those chiplets, there might be things like SerDes, DDR, and HBM Phy’s, there might be PLLs and DLLs, and all of these need to be tested. So, we can’t leave tests as an afterthought. In the past, IP vendors often ship their IP cores with just a Verilog test bench at the IP level and then left it as a user exercise to map and cycle those patterns all the way up to the top level. With 2.5D and 3D, you can imagine the additional complexity if we have that challenge. So this is essentially like adding a new level of hierarchy when we’re doing 2.5D and 3D — we’re adding kind of a hierarchy above the top level of the chip that’s incorporating all the chips, and that’s where that wrapper netlist comes in. So, IP vendors are increasingly shipping their IP cores with IJTAG. And in the IJTAG standard, there are a couple of files: The first is called ICL, which is a hardware description of the test interface, and the second is called PDL, and the PDL is like a pattern description. So, if you ship these two files and you use commercial IJTAG tools, you have the ability to generate automatically all the way up to that top level of the SiP, the test benches and production test vectors that you need to get the part going. So, that’s a very important capability that is referenced in the 3D IEEE spec, and is also its own specification called IJTAG. And then EDA vendors are also providing the IJTAG tools I alluded to that can take these all the way up to the top level through what we call retargeting. And then in other areas where IJTAG can help are things like loading large amounts of IP firmwares — for example, a SerDes might have a microprocessor or something inside of it, and to initialize the SerDes, you have to load a bunch of pretty extensive amount of data over IJTAG and start it up inside the IP. And then other areas include things like calibration procedures for high speed Phy’s, and these can be shipped to standard building blocks for IP tests while adding automation to what’s already used to be a fairly manual process in the past.

[00:18:39.27] David Lyell: We’ve had seven other podcasts for other areas of 3D IC testing. Can you talk and specify how 2.5D and 3D IC tests can be complementary to the other areas we’ve talked about?

[00:18:53.27] Joe Reynick: First we talked about power and IR drop, but another area that’s common with some of the previous podcasts like the reliability podcast are things like burn-in testing and voltage stress. So, burn-in is where we put a sample of parts into the burn-in oven — a special oven — and we raise the voltage and temperature to emulate many years of operation. So, for example, we can keep the parts inside that burning oven for up to 2000 hours, and we can emulate like 10 years of life for that part, depending on the temperature that we have. During that time, we continually run all our package-level SiP tests to provide some activity. And then we take the parts out at regular intervals to test them fully on a production tester or ATE to see if any of the parts fail. So, if any of the parts fail, then we do a failure analysis. We go to the FA lab and get those parts fixed, find out what happened, and correct it. So, reliability testing is part of that. Another one is voltage stress — it turns out that doing a voltage stress with the right voltage level for the right duration and the right ramp time can pretty closely emulate burn-in, and it has the ability to do that in just 100 milliseconds or so of production test, so you can actually do it during the production test itself. It gives you a chance to sort of degrade or destroy parts that are marginal that might fail later on. So, voltage stress is good as well for reliability testing.

[00:20:28.24] David Lyell: Thank you, Joe, for the highly informative discussion on this eighth podcast of 3D IC. We’re looking forward to future podcasts with you on the same topic. Do you have any final thoughts for our audience?

[00:20:38.10] Joe Reynick: Thanks, David, and thanks to all of our listeners for participating in our 3D IC podcast. You can access the rest of our series for other interesting discussions about many other topics, including packaging, power and reliability.

[00:20:53.08] David Lyell: Wonderful. Thank you, Joe, and we’ll talk with you next time.

[00:20:56.15] Joe Reynick: Thanks so much for your time.

About the Siemens 3D IC Design flow

The Siemens 3D IC Design Flow is a comprehensive set of tools and workflows targeted to develop advanced 2.5 and 3D IC heterogeneous system-in-package (SiP) designs. This proven, complete 3D IC design flow includes 3D architecture partitioning to planning, layout, design-for-test, thermal management, multi-die verification, interconnect IP, manufacturing signoff, and post-silicon lifecycle monitoring. Transform existing design and IP architectures into chiplets or build scalable 3D IC technology for faster time to market.

Learn more about Siemens EDA’s marketing-leading 3D IC technology solution: https://www.siemens.com/3dic