Semiconductor Packaging

Filter by:

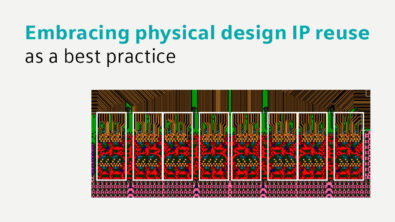

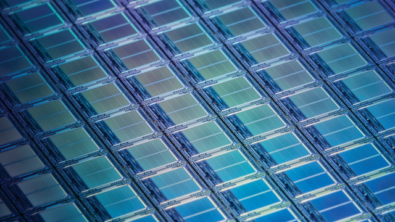

Monolithic scaling limitations drive the growth of 2.5/3D multi-chiplet, heterogeneous integration that enables PPA targets to be met. Our integrated flow addresses prototyping challenges to signoff for FOWLP, 2.5/3D IC, and other emerging integration technologies.

Learn more about semiconductor packaging design and verification.