Boost FinFET Yield with Cell-aware Scan Diagnosis

By Matt Knowles – Mentor, A Siemens Business

FinFETs display more defects at the transistor level, which also tend to be timing-related, making scan diagnosis far more difficult than in the past. Cell-aware diagnosis is the solution.

Scan diagnosis has been an important tool to find and diagnose manufacturing defects in a failing device. Being able to quickly find the root cause of a failure helps yield ramp for new manufacturing processes and squeezes out a few percent better yield for established process or high-volume ICs. To perform scan diagnosis, you need a design description, scan test patterns, and fail data from a tester to identify “suspects”, i.e. the most likely defects that caused the failures at digital test. To improve the failure analysis that is the goal of scan diagnosis, you can also add layout information to the mix.

But as the industry moves solidly into the FinFET era, product engineers are finding that the established scan test diagnosis needs an upgrade. With FinFETs, we see more front-end-of-line (FEOL) defects at the transistor level rather than in the interconnect, and fin-related defects tend to be timing-related, making physical failure analysis and yield analysis far more difficult challenges.

Mentor offers a new and powerful scan diagnosis technology, Tessent Cell-aware Diagnosis is that uses analog simulation-based fault models to diagnose timing-related cell internal defects in FinFET technology. Unlike existing scan diagnosis, this cell-aware diagnosis technology can differentiate between defects in cells and in interconnect, both static and timing-related. Cell-aware diagnosis gives yield, product, and failure analysis engineers with a tool to greatly simplify the tasks of finding defects and identifying systematic defects in FinFETs.

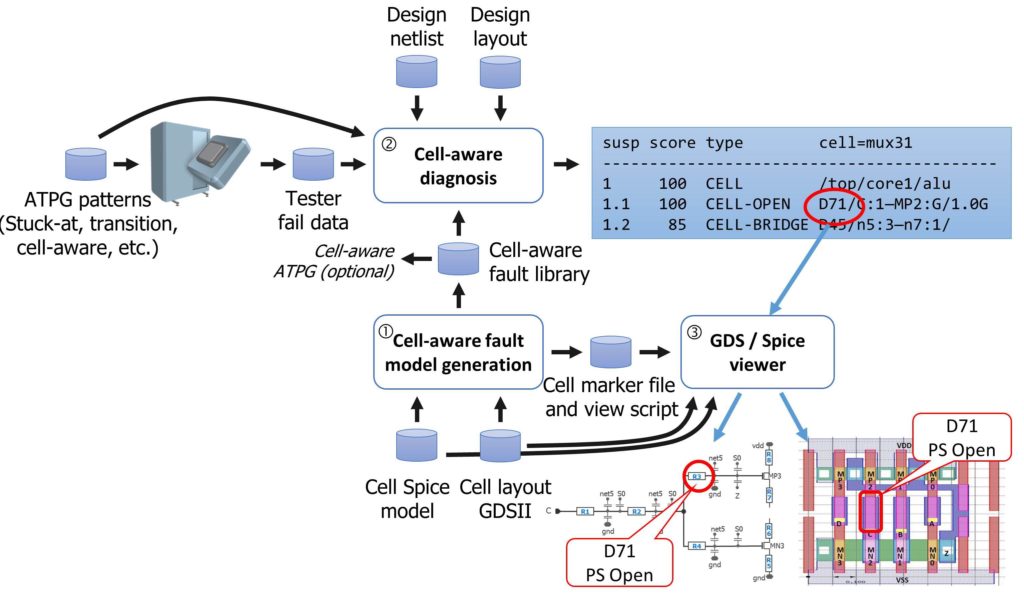

Cell-aware diagnosis is made possible by the new type of fault model created by analog simulation for all physical defects extracted from the library cell layout. The generation of the cell-aware fault model is a one-time task per technology. Once created, this fault model can be used for both test pattern generation and for diagnosis for any design based on that technology. The input to the fault model creation step is a SPICE netlist including X/Y location and layer information of each object in the SPICE netlist, or alternatively the layout file of each from which the SPICE netlist can be extracted. The outputs of this characterization step are:

- The cell-aware test and diagnosis model for all cells in the technology library

- Layout marker files for each cell to enable easy cell-level viewing of internal suspects in the layout

These models are used during diagnosis, along with the design description, tester failure data, and the test patterns. Cell-aware diagnosis works for any scan ATPG pattern type, such as stuck-at, transition delay, and cell-aware. Timing-related defect-specific issues like passing bit mismatch and glitch excitation are properly considered as well.

The cell aware diagnosis flow works just like traditional layout-aware diagnosis after the analog fault models are created. Diagnosis software considers both interconnect suspect and cell internal suspects, and then gives a comprehensive list of suspects along with layout information. The only unique step to enable cell-aware diagnosis is to also read in the cell-aware fault models. Figure 1 illustrates the cell-aware diagnosis flow.

Cell-aware diagnosis improves diagnosis quality

Cell-aware diagnosis finds the potential defect location inside the suspect cell, such as an open defect at a specific transistor, a short between two poly polygons, etc. Beyond the typical diagnosis report, Tessent cell-aware diagnosis generates a chip-level layout marker file that highlights all potential defect locations for guiding the PFA process. The cell-aware diagnosis reports can be used for volume yield analysis similarly to how traditional reports are used.

Several cell-aware diagnosis results have been published, based on technologies from 160nm down to 10nm FinFET. On average, the diagnosis resolution for cell internal defects was improved by 11.3X.

Cell-aware diagnosis for automotive

Automotive ICs use testability solutions that are otherwise reserved for more complex designs and leading edge manufacturing nodes because they must meet strict quality, reliability, and safety requirements, including high test quality, in-field self-test, and field return (RMA) analysis.

Consider large, complex cells such as adders, multipliers, and multi-bit sequential elements. Even when a defect is known to be within a cell, locating a defect in such a complex cell is daunting. Determining whether the defect is systematic or yield limiting typically requires the examination of a large number of failing die, which can take several months. Cell-aware diagnosis software dramatically improves the ability to locate specific failing transistors, a level of precision that enables automotive IC makers to comply with the strict quality, reliability, and safety standards set by OEMs and the ISO 26262 standard.

Summary

Tessent Cell-aware diagnosis has been validated successfully on several real silicon failures with known PFA results. The diagnosis resolution for cell internal defects can be improved by up to 70X on a complex full adder cell, and by over 10X on average, with a small time overhead. Cell-aware diagnosis is enabled by a layout-justified cell-aware fault model, which is generated once per library. Therefore, there is no impact on the data collection and diagnosis flow. Cell-aware diagnosis improves results for single-part diagnosis scenarios such as customer return analysis as well as volume diagnosis applications like yield analysis.

Details about cell-aware diagnosis are available in this free whitepaper Expose Transistor-level Yield Limiters with Cell-aware Diagnosis