Video: System-on-chip ATPG with Tessent SSN

At the 2023 North America User2user symposium, Intel engineer Toai Vo presented his team’s experience using Tessent Streaming Scan Network (SSN). The session was recorded and is now available for anyone to view.

Toia covers their test challenges, what led them to Tessent SSN, and how they successfully completed their first silicon design using Tessent SSN.

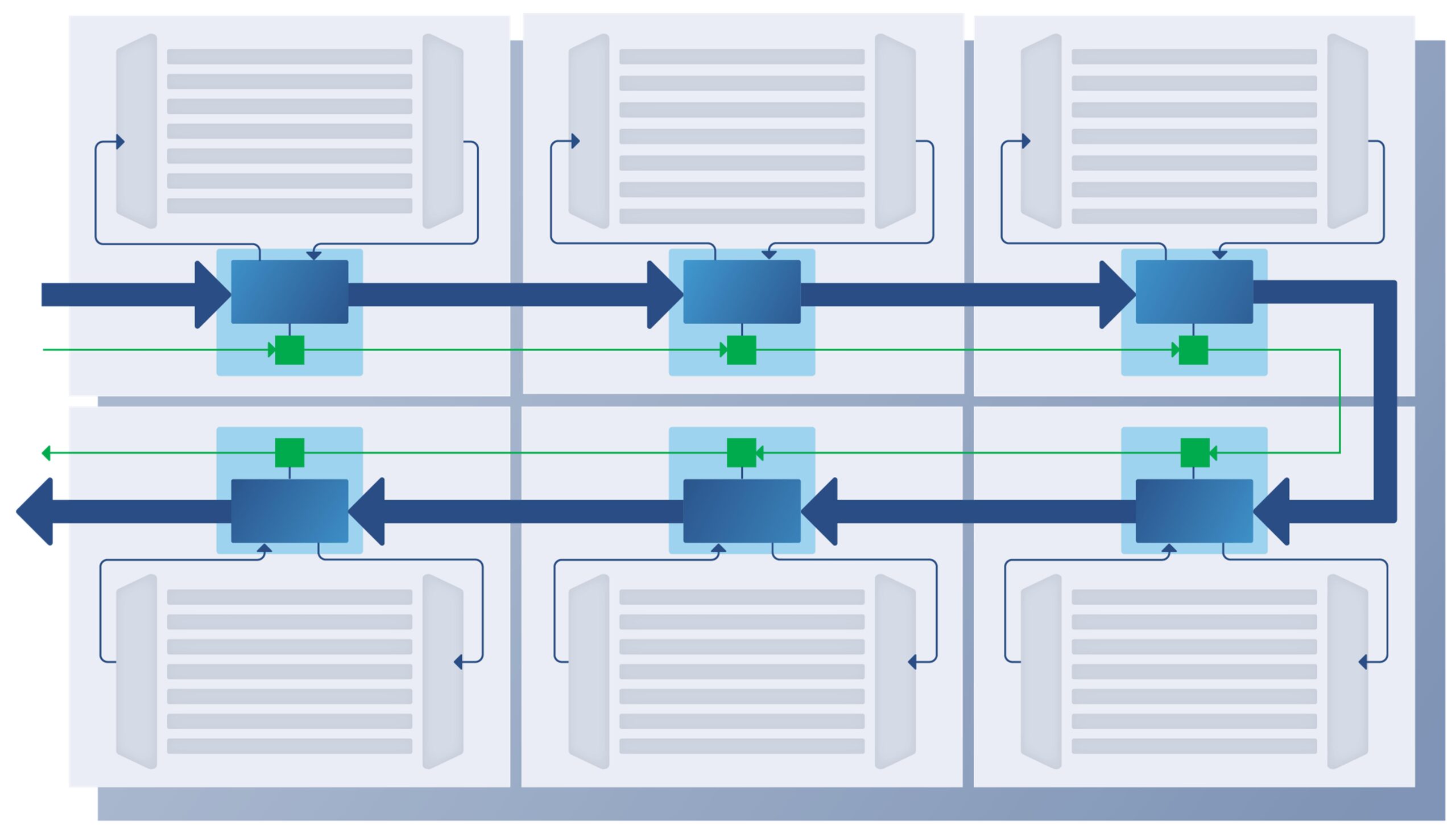

Toia’s team needed a tool and flow that would help with ATPG automation, reusability, reducing test cost, effort and time, and would also support 2.5/3D test methodology. Tessent SSN, the bus-based packetized test solution, addresses all their challenges. Tessent SSN is highly scalable and has a test infrastructure that enables reuse across device families.

With SSN, you only need to decide the data bus size at the chip level. You don’t have to worry about what’s inside the blocks. SSN is absolutely an innovative test solution. It really works!

Toai Vo, Intel

Toia’s group at Intel also liked that SSN uses the IEEE 1687 (IJTAG) network, allows easy retargeting of test patterns from block-level to chip-level, that the SSN test logic is inserted at RTL, that any number blocks can be tested concurrently to save test time.

Toai shared the results of the first silicon tests using SSN. They report a significant reduction in total test time of about 34%. Toai says the transition from traditional EDT to packet-based SSN was easy. The solution is scalable, reusable, reduces test time, and improves productivity by reducing engineering effort and silicon bring up time.

Learn more about Tessent SSN in this on-demand webinar Automation and plug-and-play DFT methods for fast time-to-market.