Faster test pattern bring-up with a desktop system

By Matthew Knowles – Mentor, A Siemens Business

Reducing the time of silicon bring-up, test pattern debug, and device characterization confers a competitive advantage for any IC company. Understanding under what conditions an IC fails and effectively isolating the problem helps design, test, and DFT engineers get the device to market faster.

The traditional process for new silicon bring-up is bogged down by a few intractable pain points:

- Managing cross-functional operations between the test engineers and the DFT engineers.

- Reserving time slots on the automatic test equipment (ATE).

- Lack of diagnosis information when reverse-mapping failure data from chip to core level.

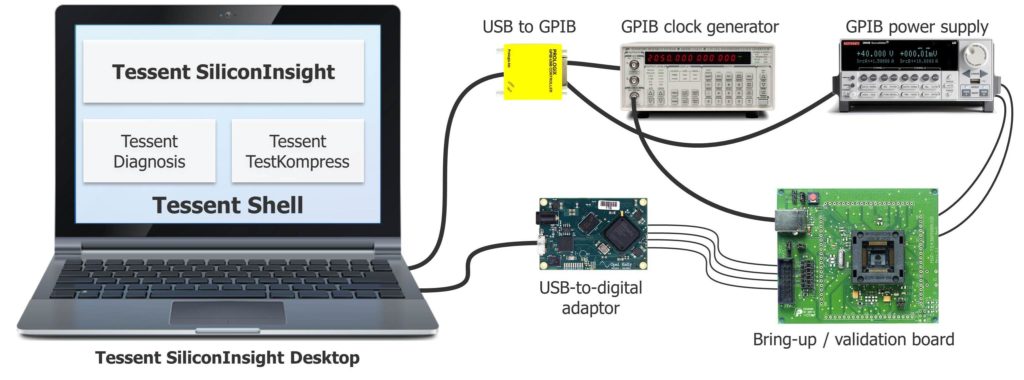

Tessent SiliconInsight Desktop can drastically reduce the overall time for silicon bring-up by using a desktop system instead of ATE to validate the patterns against the silicon.

Larger designs and smaller feature sizes create challenges along the entire IC design and test flow, including in physical failure analysis (PFA). The diagnosis process typically involves time consuming and costly roundtrip between PFA, test, and DFT engineers and access to ATE machines for silicon bring up. But this new software-led flow speeds silicon bring-up within the Tessent environment.

With Tessent SiliconInsight, you can now apply tests and capture results using the same Tessent platform that generates patterns and diagnoses failures, resulting in a reduction in bring-up time of 50% – 80% for advanced designs.

The Tessent SiliconInsight system includes a computer connected to a bring-up/validation board with the device under test (DUT). Comparable commercially available setups have until now have been limited to built-in self-test (BIST) and other test instruments accessed exclusively through the DUT’s JTAG port. With this new system, the scope is expanded to non-JTAG test access and a much wider range of pattern applications and diagnosis routines. For instance, ATPG patterns with-chip compression and over 25 external scan channels can be tested and diagnosed at the push of a button.

The benefits of using the Tessent benchtop system include significantly quicker diagnosis of the root cause of test pattern failures and lower silicon bring-up costs.

Learn how you can reduce the silicon bring-up cycle time with Tessent SiliconInsight for ATPG and an off-the-shelf hardware adaptor in this free Tessent whitepaper, Accelerating test pattern bring-up for rapid first silicon debug