ATE-Connect changes the silicon debug and bring-up flow

By Matt Knowles – Mentor, A Siemens Business

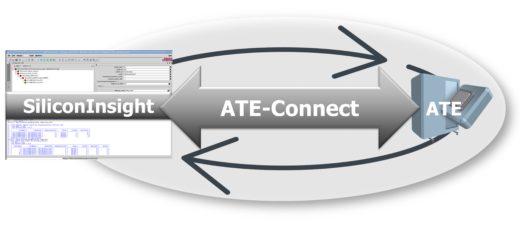

The breakthrough ATE-Connect™ technology erases the gap between automatic test equipment and DFT debug software to streamline silicon bring-up and debug.

Mentor recently announced Tessent SiliconInsight with ATE-Connect – a connection between DFT software and ATE that reduces silicon bring-up from weeks to days. It solves the key problems of IJTAG-based IP evaluation and debug. Some of the key features include:

- It can be run by the DFT engineers and designers in a protocol-based flow instead of a pattern-based flow by using IJTAG commands.

- It allows DFT engineers and designers to use their familiar Tcl-based Tessent Shell interface.

- It allows DFT engineers and designers to access ATE remotely with incremental and light-weight communication through TCP.

Today’s semiconductor market landscape calls for increasingly complex designs for 5G wireless communications, autonomous driving, and artificial intelligence applications. To manage the time and costs associated with the integration and test of increasingly large and complex designs, the industry has been rapidly adopting IJTAG (IEEE 1687) for a plug-and-play style IP integration during design. The benefits of using IJTAG are still emerging, as it allows for access and control of any embedded ‘instrument’ on a chip.

Even though IJTAG streamlines IP integration during the design phase, problems have persisted during IP evaluation and debug during silicon bring-up. Typically, the silicon bring-up process involves converting test patterns to a tester-specific format and generating a test program that is executed by ATE. Each specific chip must have test patterns written by DFT engineers and then translated by test engineers to debug each scenario on each tester type. When any of these patterns fail, the ATE output is then translated into chip failure data and sent back to the DFT engineers to be processed by diagnosis tools. It is the DFT engineers, not the ATE test engineers, who play the main role in IP evaluation and debug. The result is many long iterations that delay time-to-market.

Industry-first ATE-Connect technology

Leading chip makers need a solution to the silicon bring-up challenge. Mentor’s Tessent team created ATE-Connect technology, which creates an industry-standard interface to eliminate communication barriers between proprietary tester-specific software and DFT platforms. The result is to accelerate debug of IJTAG-compliant IP (instruments), helping speed-up product ramps, and reducing time-to-market for products in 5G wireless communications, autonomous driving, and artificial intelligence. The first ATE to fully support the new Mentor interface is the Teradyne UltraFLEX ATE with Portbridge technology.

Using the TCP/IP network protocol, ATE-Connect provides IJTAG commands to the device under test and receives data from the device on the ATE while keeping the sensitive design information in the realm of Tessent SiliconInsight, only providing the required stimulus to the device under test on the ATE. Using this standard network communication, customers can leverage their existing secure networks to enable seamless interaction with testers around the globe.

Directly linking the power of IJTAG with the ATE eliminates a significant bottleneck in the silicon debug and characterization processes, drastically reducing the average time of getting first silicon into the hands of customers.