Get on the Fast Track to Advanced Verification with UVM Express

Advanced verification techniques including functional coverage and constrained random stimulus generation have proven themselves invaluable in the design of the smallest FPGAs to the largest SoCs today. Still many design and verification teams that need to and are willing to embrace these technologies have yet to do so. Verification environments written with basic hardware description languages like Verilog and VHDL, as well as home grown environments patched together with C, Tcl, or PERL scripts are entrenched and difficult to move away from. Adopting these new techniques requires training on several fronts. You need to learn the SystemVerilog language along with Object-Oriented programming skills. And to make your verification environments reusable and interchangeable with Verification IP (VIP) that you may want to get from outside sources, you need to learn the Universal Verification Methodology (UVM).

Or do you?

Maybe you can get started by using the minimal amount of things to get started. But how can you know what you need to know when there is so much to learn? That’s where the UVM Express comes in.

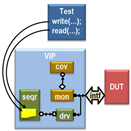

The UVM Express is a carefully planned path with a few key steps along the way to get you up and running. You learn just the things you need to be more productive at each step and advance at your own pace. There’s no need to digest everything at once to get up and running. The UVM Express path has four key steps:

Step #1 Organize your Testbench into a BFM

- Use a SystemVerilog Interface to group your Signals

- Write your test in terms of transactions

- Call tasks to execute transactions

Step #2 Add Functional Coverage

- Use Metrics to check Verification quality- How good are your tests?

- Add coverage agents

- Leverage pre-built VIP in passive mode

Step #3 Add Constrained Random Stimulus

Improve your test quality by generating stimulus efficiently

Improve your test quality by generating stimulus efficiently- Leverage pre-built VIP in active mode

Step #4 Use the full power of the UVM

- Modify your environment to improve reusability and configurability

- Leverage all your code from the previous steps

The UVM Express adds to the many guides and examples in the UVM/OVM Online Methodology Cookbook on the Verification Academy. There is also a new UVM Express module that provides a multi-media walk through each of the steps. You can discuss this with me at next week’s DVCon 2012.