Part 10: The 2018 Wilson Research Group Functional Verification Study

IC/ASIC Language and Library Adoption Trends

This blog is a continuation of a series of blogs related to the 2018 Wilson Research Group Functional Verification Study (click here). In my previous blog (click here), I examined IC/ASIC project verification technology adoption trends. In this blog I plan to discuss various IC/ASIC language and library adoption trends.

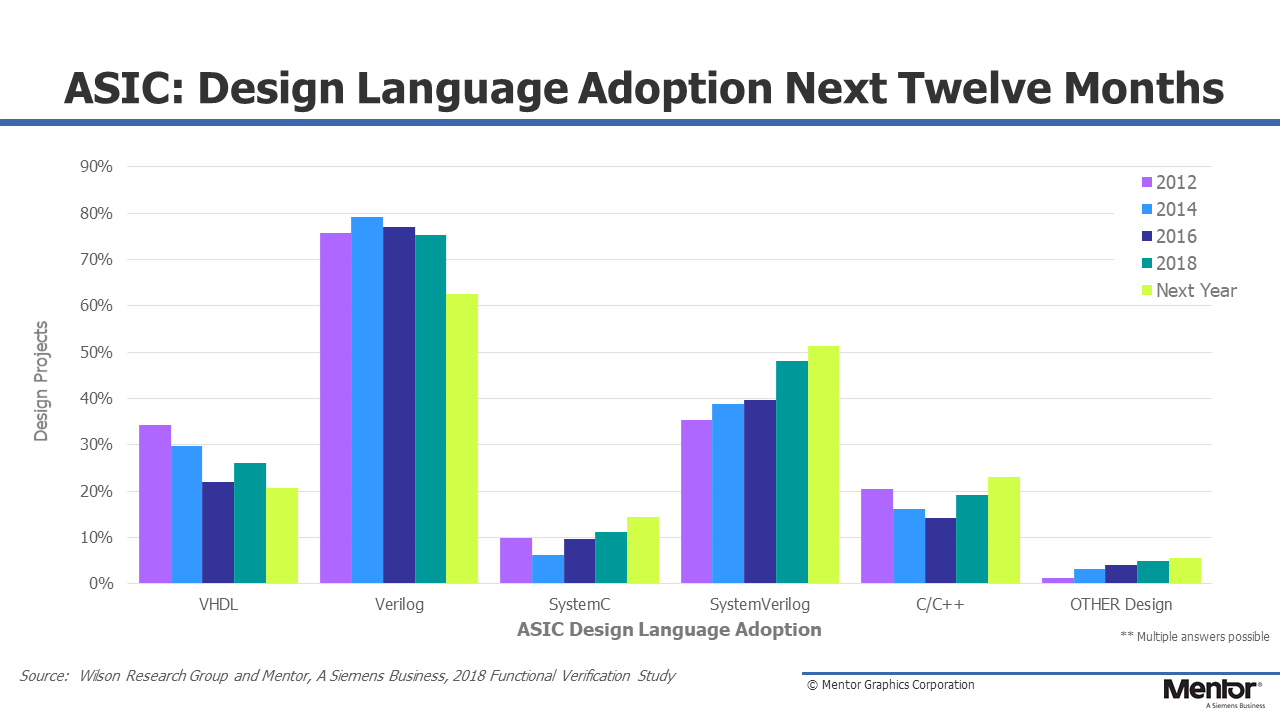

Figure 10-1 shows the aggregated adoption trends for languages used to create RTL designs across all market segments and all regions of the world. We see continual interest in SystemVerilog for RTL creation.

Figure 10-1. IC/ASIC Languages Used for RTL Design

It is not uncommon for IC/ASIC projects to use multiple languages when constructing their testbenches. This practice is often due to legacy code as well as purchased verification IP. This is the reason that the results in Figure 10-1 sum to more than 100 percent.

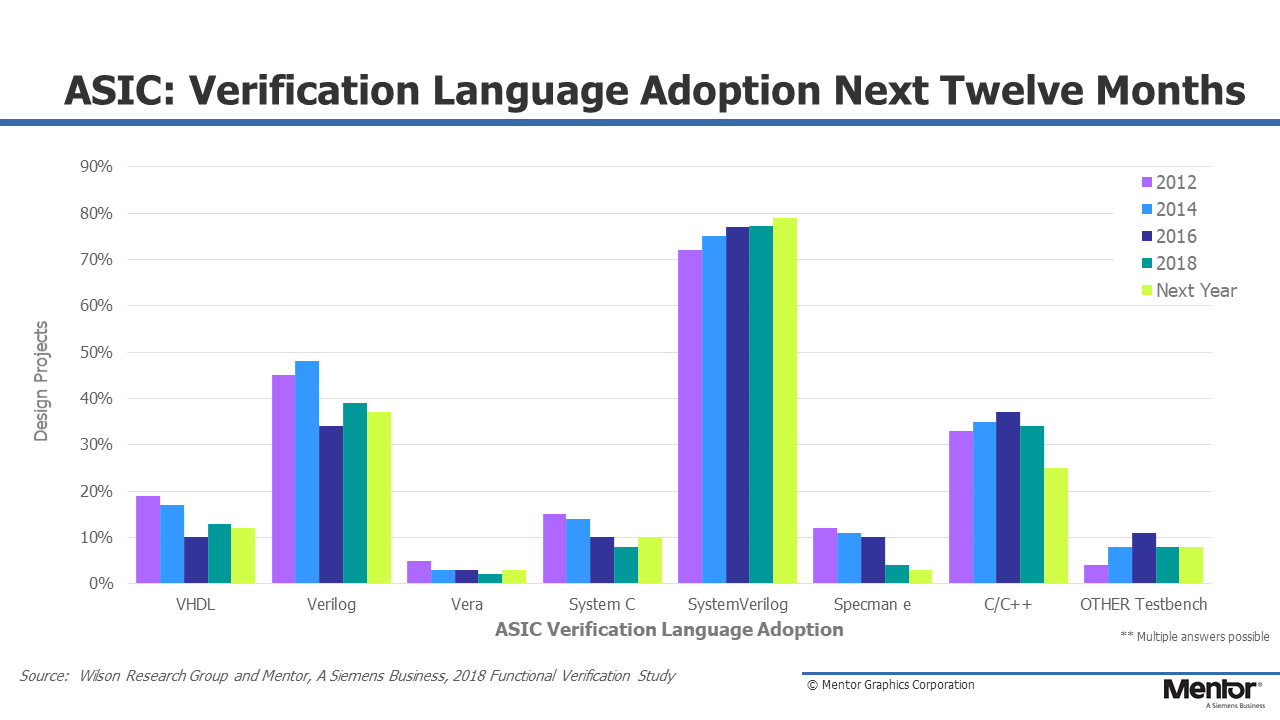

Figure 10-2 shows the adoption trends for languages used to create IC/ASIC testbenches. The data suggest that the adoption rates for all languages used to create testbenches are either declining or flat. As I mentioned in Part 7 of this blog series (click here), we are seeing a continual increase in design projects working on designs less than 100K gates, which is an additional factor we need to consider when examining the findings in Figure 10-2. This can yield some interesting results in the study. The reason for this is that these very small projects typically do not apply advanced verification techniques, which can bias the overall industry verification technique adoption trends in some cases to appear as flat or declining. However, even factoring this bias into the results we find that SystemVerilog adoption is still starting to saturate or level off in the upper-70s range since most IC/ASIC projects are mature in their simulation processes for IP and subsystem verification.

Figure 10-2. IC/ASIC Languages Used for Verification (Testbenches)

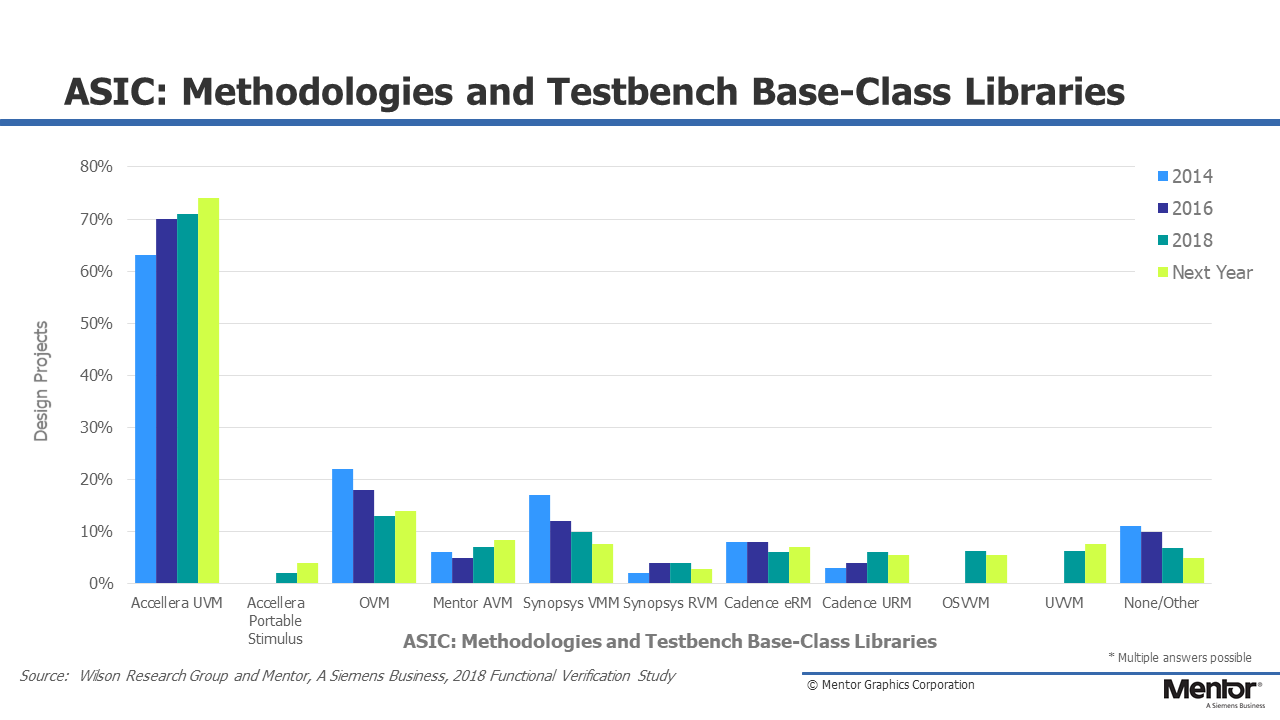

Figure 10-3 shows the adoption trends for various IC/ASIC testbench methodologies built using class libraries.

Figure 10-3. IC/ASIC Methodologies and Testbench Base-Class Libraries

Here we see a decline in adoption of all methodologies and class libraries with the exception of Accellera’s UVM, whose adoption continued to increase between 2014 and 2018. Furthermore, our study revealed that UVM is projected to continue its growth over the next year. However, like SystemVerlog, it is expected to saturate or level off in the mid- to upper-70 percent range.

Note, for the first time we asked the question concerning the new Accellera Portable Test and Stimulus Standard (PSS). It is important to keep in mind that PSS was officially approved in late June 2018, and our study had started prior to its approval. We should be able to get a better sense of its true adoption rate with our next study.

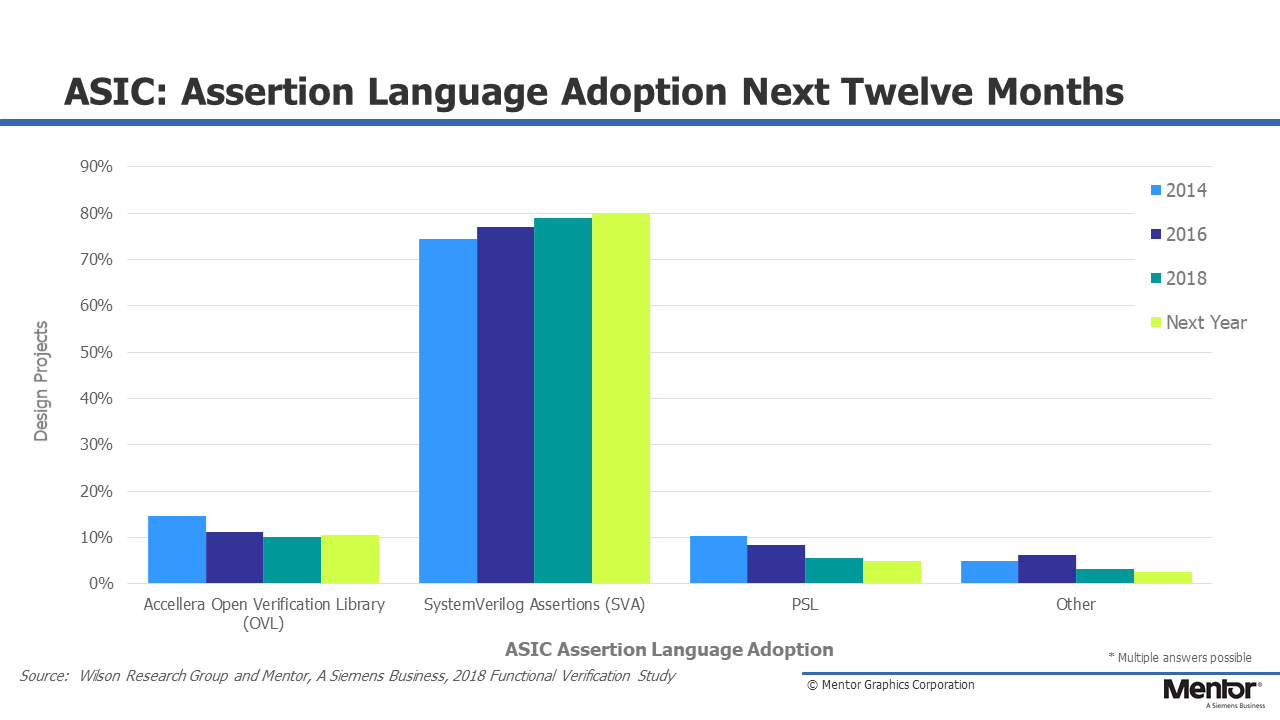

Figure 10-4 shows the IC/ASIC industry adoption trends for various assertion languages, and again, SystemVerilog Assertions seems to have saturated or leveled off. This is just another indication of a mature industry, which has adopted standard processes for IP and subsystem verification.

Figure 10-4. IC/ASIC Assertion Language Adoption

In my next blog (click here) I plan to present the IC/ASIC design and verification power trends.

Quick links to the 2018 Wilson Research Group Study results

- Prologue: The 2018 Wilson Research Group Functional Verification Study

- Understanding and Minimizing Study Bias (2018 Study)

- Part 1 – FPGA Design Trends

- Part 2 – FPGA Verification Effectiveness Trends

- Part 3 – FPGA Verification Effort Trends

- Part 4 – FPGA Verification Effort Trends (Continued)

- Part 5 – FPGA Verification Technology Adoption Trends

- Part 6 – FPGA Verification Language and Library Adoption Trends

- Part 7 – IC/ASIC Design Trends

- Part 8 – IC/ASIC Resource Trends

- Part 9 – IC/ASIC Verification Technology Adoption Trends

- Part 10 – IC/ASIC Language and Library Adoption Trends

- Part 11 – IC/ASIC Power Management Trends

- Part 12 – IC/ASIC Verification Results Trends

- Conclusion: The 2018 Wilson Research Group Functional

Comments