Getting Organized with SystemVerilog Arrays

SystemVerilog has many ways to store your data. Vectors, arrays, structures, classes, and probably several more ways that I don’t remember. There are too many choices to squeeze into even 10 blog posts, so I made a webinar, actually two of them, to help you get organized.

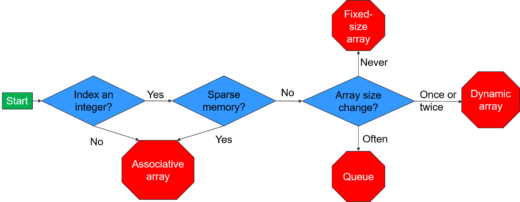

The first webinar focuses on vectors, fixed size arrays, dynamic arrays, queues, associative arrays, and strings. (Yeah, that’s one I forgot.) Here is a sneak peek – a diagram to help you choose between these different types.

Ever stumble across the following code and wondered what it does?

q = array.find(x) with (x>5);

Looks like it is trying to find something greater than 5, but what is that ‘x’ for, and why does searching an array produce a queue? Sign up for the webinar with the full explanation. It is Friday June 5 at 8:15am PDT. I’m starting a little later so you can grab another cup of coffee before joining, or give your home-school kid some breakfast. No problem if you can’t make it as these are all recorded.

Enjoy your verification journey!

Chris Spear

Keep learning at mentor.com/training

Questions or ideas? verificationacademy.com/ask-chris-spear

View my recent webinar on UVM Coding Guidelines and the Questions and Answers