Portable and Productive Test Creation with Graph-Based Stimulus

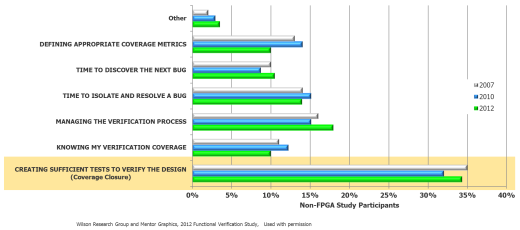

Verification engineers spend lots of time creating tests. In fact, creating enough tests to verify the design functionality consistently tops the list of verification challenges, according to periodic surveys of our customers.

One challenge in test creation is that verification occurs in multiple environments. For high-level models, verification might be performed in a SystemC environment. Unit-level verification often occurs in a SystemVerilog UVM environment. At the SoC level, the presence of embedded processor cores means embedded software must be part of the verification picture.

Writing specific tests for each environment only exacerbates the “creating enough tests” problem. Besides, different environments offer different levels of automation for test creation. For example, embedded software environments offer no help in creating tests more productively or creating more comprehensive tests – it’s directed tests all the way.

Portable graph-based stimulus brings advanced and highly-productive stimulus modeling techniques to a wide range of verification languages and environments – from automating sequences and virtual sequences in SystemVerilog to creating automated stimulus in VHDL. From verifying C and SystemC designs for high-level synthesis to automating software-driven test scenarios running on embedded processor cores.

If you are attending either DVCon India or DVCon Europe and are interested in how graph-based portable stimulus can boost your test-creation productivity, please consider attending the graph-based portable stimulus tutorial. Links to the respective conference programs are below.

DVCon India Conference Program: http://dvcon-india.org/conf/program-at-a-glance/

DVCon Europe Conference Program: http://dvcon-europe.org/wp-content/uploads/2014/09/dvcon-europe-advance-program-9-4-2014.pdf

Comments