Asking better questions on the Verification Academy Forums with EDAPlayground

The forums on the Verification Academy have been around for about a decade (even longer if you count its origins from OVMWorld). At the recent DVCon’s in the US and India, many people came up to greet me and shared their stories of how they had a problem and found a solution on the forum. A significant number of them had never posted a question. They just searched for similar problems with answers. That’s perfectly fine and a great example of re-use.

On the other extreme, many people post questions without thinking about how other people could read it. Many of us are experts in our respective fields and it’s hard to remember a time when we couldn’t understand what seems trivial to us today, myself included🧔🏻. Over the years I’ve seen what it takes to ask a good question. There are now many good write-ups on how to ask a good question (e.g. here and here). After a long absence, Questa is now available on the  EDAplayground along with Precision synthesis. Let me explain how to use these tips and tools to ask better questions on the Verification Academy forums.

EDAplayground along with Precision synthesis. Let me explain how to use these tips and tools to ask better questions on the Verification Academy forums.

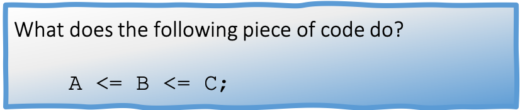

Here’s a common type of beginner’s question (asked by a number of people so I’m not picking on you specifically):

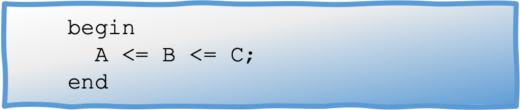

In SystemVerilog, the context of where an expression is located can change its meaning. So if I saw code in question was inside a procedural block as:

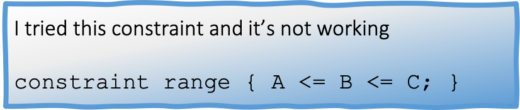

I’d at least know that this is a non-blocking assignment to A with the right-hand-side expression B less-than-or-equal to C. But other times this question gets asked as:

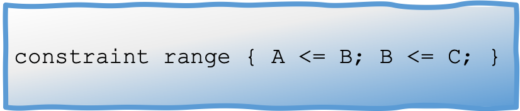

We don’t know what “not working” means. Does it not compile? Does the constraint fail? Are you getting results you are not expecting? A simple little test case on EDAPlayground that shows actual results with an explanation of why those results are not what you are expecting helps tremendously. After looking at the output from EDAPlayground: ‘{A:3, B:1, C:4}, I can see that those values satisfy the constraint because the expression gets evaluated as (A <= B) <= C; Substituting those values we have 3’d3 <= 3’d1 is 1’b0, and 1’b0 <= 3’d4 is 1’b1, so the solver is able to pick those values as a solution. What you probably intended to write was:

I hope this demonstrates how you can easily add just a few extra lines in your question helping others get right to the point of your question. It’s even easier to discuss one’s issues and share what you mean by small code examples via EDAPlayground just as I did with my simple little test case. And do read the link on creating a minimal example. Hopefully you’ll get better answers from asking better questions. (Emphasis on small, simple and minimal – get right to the point without other distractions)

-dave_rich 🧔🏻