Part 6: The 2020 Wilson Research Group Functional Verification Study

FPGA Language and Library Trends

This blog is a continuation of a series of blogs related to the 2020 Wilson Research Group Functional Verification Study. In my previous blog, I discussed FPGA verification techniques and technologies adoption trends, as identified by the 2020 Wilson Research Group study. In this blog, I’ll present FPGA design and verification language adoption trends.

It is not uncommon for FPGA projects to use multiple languages when constructing their RTL and testbenches. This practice is often due to legacy code as well as purchased IP. Hence, you might note that the percentage adoption for some of the languages that I present sums to more than one hundred percent.

When reviewing the language adoption trends, it is important to keep in mind potential regional biases influencing this year’s findings as previously discussed in my blog Understanding and Minimizing Study Bias (2020 Study).

FPGA RTL Design Language Adoption Trends

Let’s begin by examining the languages used to create FPGA RTL designs. Figure 6-1 shows the trends in terms of languages used for design, by comparing the 2012, 2016, and 2020 Wilson Research Group study, as well as the projected design language adoption trends within the next twelve months.

It is important to note that the language adoption trends shown in fig. 6-1 are aggregated across all market segments and all regions of the world. When we filter the participants down to a specific region (e.g., Europe), or a specific market segment (e.g., Mil/Aero), then the adoption percentages are different. Yet, it is still useful to examine worldwide trends to get a sense of where the overall industry is moving in the future in terms of design ecosystems.

FPGA RTL Verification Language Adoption Trends

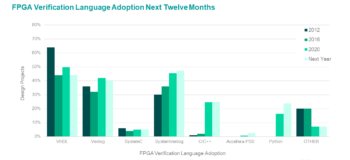

In fig. 6-2, we show the adoption trends for languages to build testbenches.

Historically, VHDL was the predominant language used for FPGA testbench development, but we have recently seen increasing interest in SystemVerilog adoption. Today, it is not unusual to find that the RTL design was created using VHDL, and the testbench was created using SystemVerilog.

This year we started tracking Python for testbench development, which is why we are not showing trends here. Also notice the large increase in C/C++ adoption for testbench development, which is often a key element in SoC-class verification as well as algorithm development.

FPGA Testbench Methodology Class Library Adoption Trends

The adoption trends for various base-class library and methodology standards are shown in Fig. 6-3, and we found that the Accellera UVM is currently the predominant standard that has been adopted to create FPGA testbenches worldwide.

As I previously stated, if you were to filter the results down by a particular market segment or region of the world, you would find different results.

For our 2020 study, we track Python-based methodologies, such as cocotb, for the first time as shown.

In fig. 6-4., we are showing trends between 2018 and 2020 for the Open Source VHDL Verification Methodology™ (OSVVM) and the Universal VHDL Verification Methodology (UVVM).

FPGA Assertion Language and Library Adoption Trends

Finally, FPGA project adoption trends for various assertion language standards are shown in Fig. 6-5, where SystemVerilog Assertions (SVA) is the predominant assertion language in use today. Similar to languages used to build testbenches, it is not unusual to find FPGA projects create their RTL in VHDL and then create their assertions using SVA.

In my next blog, I will shift the focus from FPGA trends and start to present the IC/ASIC findings from the 2020 Wilson Research Group Functional Verification Study.

Quick links to the 2020 Wilson Research Group Study results

- Prologue: The 2020 Wilson Research Group Functional Verification Study

- Understanding and Minimizing Study Bias (2020 Study)

- Part 1 – FPGA Design Trends

- Part 2 – FPGA Verification Effectiveness Trends

- Part 3 – FPGA Verification Effort Trends

- Part 4 – FPGA Verification Effort Trends (Continued)

- Part 5 – FPGA Verification Technology Adoption Trends

- Part 6 – FPGA Verification Language and Library Adoption Trends

- Part 7 – IC/ASIC Design Trends

- Part 8 – IC/ASIC Resource Trends

- Part 9 – IC/ASIC Verification Technology Adoption Trends

- Part 10 – IC/ASIC Language and Library Adoption Trends

- Part 11 – IC/ASIC Power Management Trends

- Part 12 – IC/ASIC Verification Results Trends

- Conclusion: The 2020 Wilson Research Group Functional

- Epilogue: The 2020 Wilson Research Group Functional Verification Study

Comments