Introducing UVM Connect

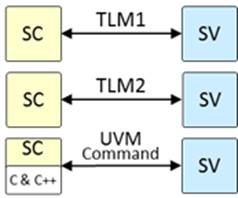

In his recent post on UVM: Some Thoughts Before DVCon, Dennis outlined some great ideas about what we think should happen next for UVM. His 3rd point, “UVM needs to bridge the system domain,” is particularly relevant given the newly-formed Accellera Systems Initiative. This is actually an area we’ve been contemplating for a while here at Mentor, and as Dennis indicated, we shared our thoughts on this topic at our last face-to-face with the VIP-TSC. With demand coming from our users, and some positive feedback on our proposal, we have just released UVM Connect, an open-source library that provides TLM1 and TLM2 connectivity and object passing between SystemC and SystemVerilog models and components, as well as a UVM Command API for accessing and controlling UVM simulation from SystemC (or C or C++).

You can find much more information on the UVM Connect page of Verification Academy.

Mentor has always believed that SystemVerilog and SystemC each have their own strengths and that the most productive way to combine them in a system-level environment is to preserve the strengths of each while allowing the free exchange of data between them. Instead of trying to re-implement UVM in SystemC, or to extend SystemC to try and recreate SystemVerilog functional coverage or constrained-random stimulus, UVM Connect provides the framework needed to interoperate between languages. This lets you:

- Reuse your SystemC architectural models as reference models in UVM verification

- Reuse your stimulus generation agents in SystemVerilog to verify models in SystemC

- Have access to a wider array of VIP since you are no longer confined to a single language

- Utilize and interact with the UVM infrastructure from SystemC, including wait for and control UVM phase transitions, set and get configuration, issue UVM-style reports, set factory type and instance overrides, and more

UVM Connect provides object-based data transfer across the language boundary via TLM1 and TLM2 interfaces, which are natively supported in both languages. It works out-of-the-box with UVM 1.1a and later and lets you use your existing TLM models, regardless of language, in a mixed-language context without modification. In a nutshell, UVM Connect fulfills the principles and purpose of the TLM interface standard, letting you design independent models that communicate without directly referring to each other. The models thus work equally well in both native and mixed-language environments.I encourage you to download the kit and give it a try. In the spirit of “co-op-etition” I also encourage our competitors to qualify the library on their simulators.

In addition to the great material in the UVM/OVM Online Methodology Cookbook on Verification Academy, the kit also includes an HTML User’s Guide, based on extensive, well-documented examples, that includes detailed information on all aspects of the API. Please make sure to stop by the Mentor booth at DVCon and let us know what you think.

Comments

Leave a Reply

You must be logged in to post a comment.

This is a much needed solution to how verification would be accomplished going forward. Constrained random verification using standards is sweet spot for UVM. Modeling at various level of abstraction (form LT to AT and various shades in between) has been sweet spot for SystemC. More and more future designs would increasingly have hybrid models; UVM connect is a great enabler.